资料下载

×

跨导运算放大器应该如何设计实例详细说明

消耗积分:3 |

格式:pdf |

大小:0.32 MB |

2019-12-31

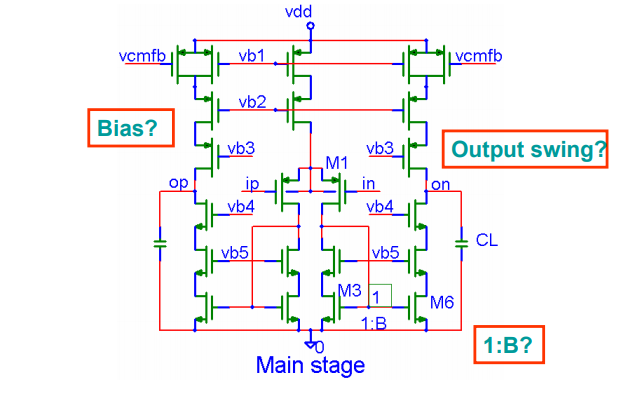

所设计的OTA要应用于课程设计10bit cyclic ADC中。在开关电容ADC中,ADC的速度取决于级电路的建立速度,而级电路的建立过程可视为由大信号压摆区和小信号线性建立区构成,其中,小信号建立区的时间通常要占到总建立时间的80%~90%,因此,OTA的大信号压摆率对ADC的速度影响较小;

从另一个方面来说,压摆率只取决于偏置电流,当偏置电流和电容确定后,无论输入管的VGS-VT是大是小,压摆率都不变。对于连续信号处理电路,我们希望 OTA在整个设计带宽内工作时,输出信号不会因为摆率跟不上而幅度受限,这个时候需要SR/GBW大一些,即输入管的VGS-VT大一些;但是,对于采样信号处理电路,比如我们所要设计的ADC,当我们确定好偏置电流,然后降低输入管的 VGS-VT,这个时候,SR不变,GBW变大,即SR/GBW变小了,而最终的建立时间反而缩小了,ADC的速度加快了。因此,SPEC中没有提出对SR的具体要求。

注意:不同应用对SR/GBW的不同要求!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章