资料下载

×

硬件EMC的设计规则详细说明

消耗积分:2 |

格式:pdf |

大小:0.29 MB |

2020-11-25

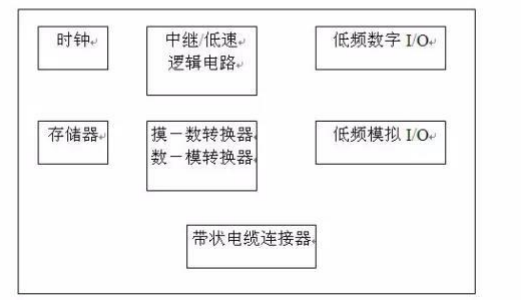

电磁干扰的三要素是干扰源、干扰传输途径、干扰接收器。EMC 就围绕这些问题进行研究。最基本的干扰抑制技术是屏蔽、滤波、接地。它们主要用来切断干扰的传输途径。广义的电磁兼容控制技术包括抑制干扰源的发射和提高干扰接收器的敏感度,但已延伸到其他学科领域。本规范重点在单板的 EMC 设计上,附带一些必须的 EMC 知识及法则。在印制电路板设计阶段对电磁兼容考虑将减少电路在样机中发生电磁干扰。问题的种类包括公共阻抗耦合、串扰、高频载流导线产生的辐射和通过由互连布线和印制线形成的回路拾取噪声等。

在高速逻辑电路里,这类问题特别脆弱,原因很多:

1、电源与地线的阻抗随频率增加而增加,公共阻抗耦合的发生比较频繁;

2、信号频率较高,通过寄生电容耦合到步线较有效,串扰发生更容易;

3、信号回路尺寸与时钟频率及其谐波的波长相比拟,辐射更加显著。

4、引起信号线路反射的阻抗不匹配问题。

1、总体概念及考虑

1、五一五规则,即时钟频率到 5MHz 或脉冲上升时间小于 5ns,则 PCB 板须采用多层板。

2、不同电源平面不能重叠。

3、公共阻抗耦合问题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章