资料下载

Xilinx 7系列FPGA SelectIO IDDR的操作模式详细概述

在7系列设备的ILOGIC block中有专属的registers来实现input double-data-rate(DDR) registers。这些特性可以通过实例化IDDR 原语实现。

所有进入到I/O tile 的clocks都是完全多路复用的,即在ILOGIC和OLOGIC之间没有clock sharing。 IDDR原语支持如下的操作模式:

• OPPOSITE_EDGE mode

• SAME_EDGE mode

• SAME_EDGE_PIPELINED mode

在Virtex-6架构中,SAME_EDGE和SAME_EDGE_PIPELINED模式是一样的。这些模式允许设计者在ILOGIC block中把falling edge的data传输到rising edge domain里,节省CLB和clock resources,而且提高了性能。这些模式用DDR_CLK_EDGE定语可以实现。下面介绍详细介绍这些模式。

OPPOSITE_EDGE 模式

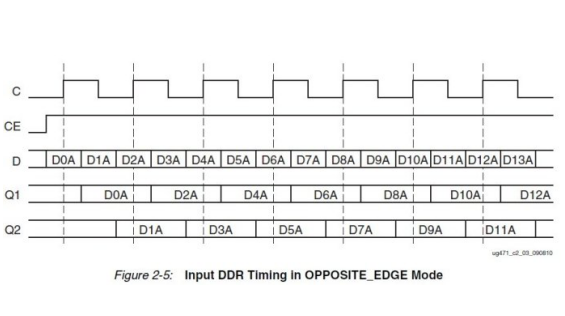

一个传统的DDR solution或者叫OPPOSITE_EDGE模式,通过在ILOGIC block中的一个single input完成的。输出Q1在clock的上升沿,Q2在clock的下降沿时,data输出到FPGA里。这个结构和Virtex-6 FPGA类似。下图显示了使用OPPOSITE_EDGE模式时,input DDR的时序图。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章