资料下载

×

Xilinx IDDR原语时序图的详细资料说明

消耗积分:0 |

格式:rar |

大小:0.13 MB |

2020-12-28

传统的输入DDR解决方案或OPPOSITE_EDGE模式是通过ILOGIC模块中的单个输入实现的。 数据在时钟的上升沿通过输出Q1提供给FPGA逻辑,在时钟的下降沿通过输出Q2提供给FPGA逻辑。 该结构类似于Virtex-6 FPGA实现。 图1 显示了使用OPPOSITE_EDGE模式的输入DDR的时序图。

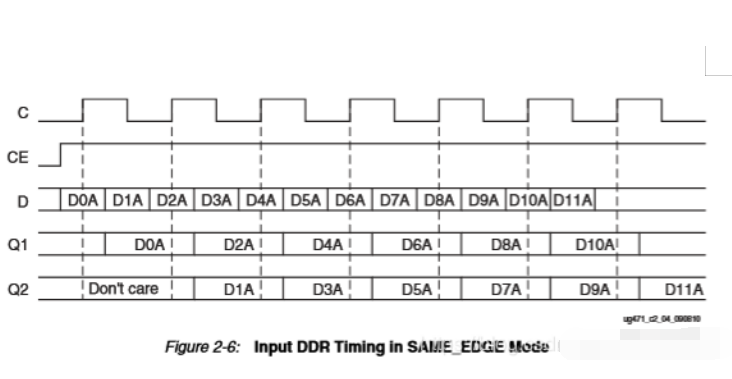

SAME_EDGE Mode

在SAME_EDGE模式下,数据在同一时钟边沿上呈现给FPGA逻辑。 该结构类似于Virtex-6 FPGA实现。

图2显示了使用SAME_EDGE模式的输入DDR的时序图。 在时序图中,输出对Q1和Q2不再是(0)和(1)。 相反,第一对呈现的是Q1(0)和Q2(不关心),然后是下一个时钟周期的对(1)和(2)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章