资料下载

×

使用VHDL实现数字电路设计的详细资料说明

消耗积分:0 |

格式:rar |

大小:1.18 MB |

2021-01-21

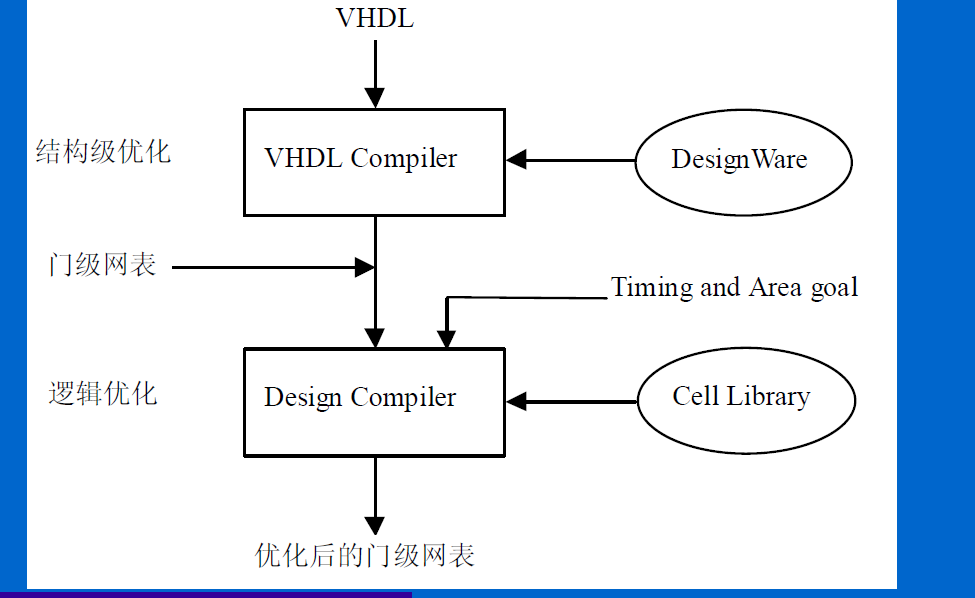

本文档的主要内容详细介绍的是使用VHDL实现数字电路设计的详细资料说明包括了:ASIC技术的发展,电路系统设计方法,自定向下的设计流程,设计描述风格。

由于所设计的系统的规模已从几十几百门增加到几万几十万门,使得从前电子工程师所熟悉的画电路图、真值表和卡诺图的设计方法已经远远不能满足数字系统的复杂性要求

高层次设计方法──HLD(High Level Design)是从八十年代末以来,最新专用集成电路设计的、最先进的设计方法,它为用户设计更大规模、更高水平、性能优良的数字系统提供了可靠的保证

HLD符合目前对电路的两个要求

Time to MarketiteaokTmM :对于通信领域来说,快速推出市场需要的系统具有非常重要的价值,HLD使得快速设计较大的芯片成为可能。

SOC:目前对数子系统的需求是规模越来越大,HLD非集成电路专业背景的通信厂商设计大规模芯片提供了可能

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章