资料下载

×

VHDL的硬件描述语言基础详细资料说明

消耗积分:0 |

格式:rar |

大小:0.34 MB |

2021-01-21

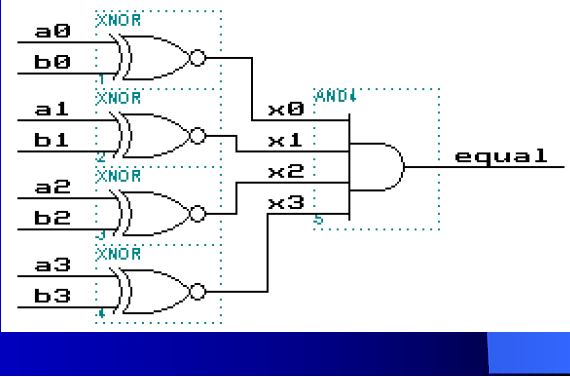

本文档的主要内容详细介绍的是VHDL的硬件描述语言基础详细资料说明包括了:简介,基本结构,基本数据类型,设计组合电路,设计时序电路,设计状态机,大规模电路的层次化设计,Function and Procedure

传统数字电路设计方法不适合设计大规模的系统。工程师不容易理解原理图设计的功能。

众多软件公司开发研制了具有自己特色的电路硬件描述语言( Hardware DescriptionLanguage,HDL),存在着很大的差异,工程师一旦选用某种硬件描述语言作为输入工具,就被束缚在这个硬件设计环境之中。因此,硬件设计工程师需要一种强大的、标准化的硬件描述语言,作为可相互交流的设计环境。

用于设计复杂的、多层次的设计。支持设计库和设计的重复使用

与硬件独立,一个设计可用于不同的硬件结构,而且设计时不必了解过多的硬件细节。

有丰富的软件支持VHDL的综合和仿真,从而能在设计阶段就能发现设计中的Bug,缩短设计时间,降低成本。

更方便地向ASIC过渡

VHDL有良好的可读性,容易理解。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章