资料下载

×

如何使用FPGA实现高性能全数字锁相环的设计

消耗积分:0 |

格式:rar |

大小:0.34 MB |

2021-01-26

本文提出了一种适用范围广泛的全数字锁相环(ADPLL)实现方法.在锁相环输入频率未知的情况下,实现锁相锁频功能。本文从全数字锁相环的基本实现方式入手.进行改进,并使用VH DL语言建模,使用FPGA进行验证。

1、引言

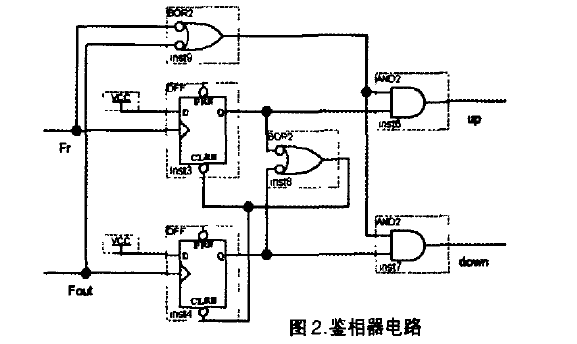

锁相环是一个能自动跟踪输入信号相位的闭环自动控制系统,其基本组成包括:鉴频,鉴相器,环路滤波器。压控振荡器以及分频器,这几个部分一起构成一个负反馈环路。实现被锁信号和参考信号的相位同步。

锁相环应用领域十分广泛。而随着集成电路发展。全数字的锁相环在通信系统中也被广泛应用。随着集成电路的发展,锁相环功能被集成在电路芯片内,可以直接配置调用。许多FPGA可以直接调用IP。生成非常合适芯片构造的锁相环,但是对于输入(被锁)频率未知的情况并不适用。基于此,本文设计了一种适合于锁定未知频率的锁相环。重点分析并实现鉴频模块电路,并且分析了ADPLL中LFSR计数器的使用和鉴相器的改进。由于设计的合理性。降低了FPGA上关键路径的组合逻辑规模,改善了锁相环中的时钟偏移,提高了系统在FPGA上实现的速度,很大程度上满足了ADPLL的高性能要求,非常适合于高速情况下的应用。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章