资料下载

×

基于FPGA的运动图像编码器的设计方案

消耗积分:0 |

格式:pdf |

大小:未知 |

2021-03-09

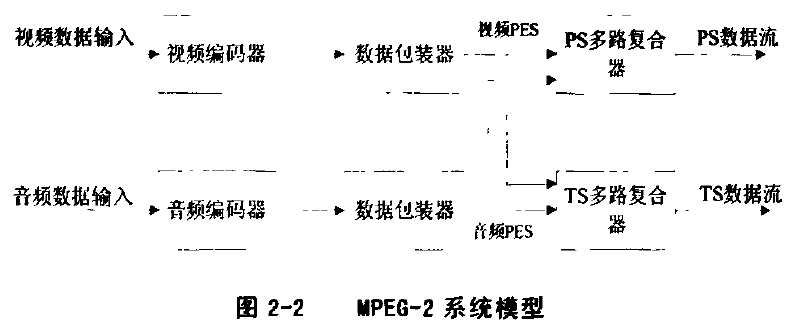

现场可编程门阵列(FFGA)具有使用灵活、体系结构可变、价格低廉执行速度快等优点,很好地适应了现代远程教育中的多元化需求。因此,本文从经济实用的角度出发,为山区、偏远农村现代远程教育,设计了一种基于FPGA的经济型MPEG-2运动图像编码器的IP核。

本文在现代远程教育需求与运动图像编码标准MPEG2的交叉点选题,针对山区、偏远农村现代远程教育这一特定的应用领域,开发基于FPGA的经济型MPEG-2运动图像编码器IP核上进行了一些探索和研究。论文针对FPGA设计特点以及本系统的应用环境,采用HDL语言自顶向下设计了MPEG-2编码器中的核心部分的ⅠP核,重点解决了其中的二维DCT模块、可变字长编码模块当中的关键路径时延过大的问颞,提高了系统的最大工作频率,并且对运动估计模块采用了一种高度并行及紧凑流水线技术的运动估计电路结构,通过改进搜索窗缓存、PE运算阵列等单元,获得了较高的运算速度增益并有效地降低了电路功耗。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章