资料下载

×

如何使用嵌入式FPGA实现RS-CC的级联编码器设计

消耗积分:0 |

格式:zip |

大小:0.39 MB |

2021-02-01

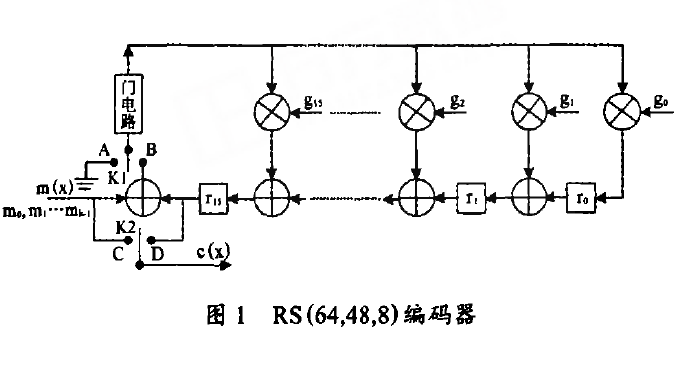

分析了802.16e无线通信系统,针对设计过程中经常出现的数据信息不同步问题,提出了一种基于RS(64,48.8)+cc(2,1,7)+交织的级联编码设计方案。该方案利用功能模块化的设计理念,达到了在不增加译码复杂度的情况下实现有效而可靠的通信.通过将各级编解码模块化,利用FPGA技术实现了整个级联纠错编译码系统.实验结果表明,模块化的FPGA嵌入式设计不仅提高了系统的稳定性,还大大缩短了开发周期.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章