资料下载

带有初始化信号的0-9加/减计数器

描述

目标:该项目的主要目标是展示高级综合设计流程在实现数字系统中的能力和能力。

由于这是我在 hackster 中的第一个项目,因此我尝试逐步解释所有细节。如果您有兴趣学习高级合成技术来设计数字系统,请参阅此处。

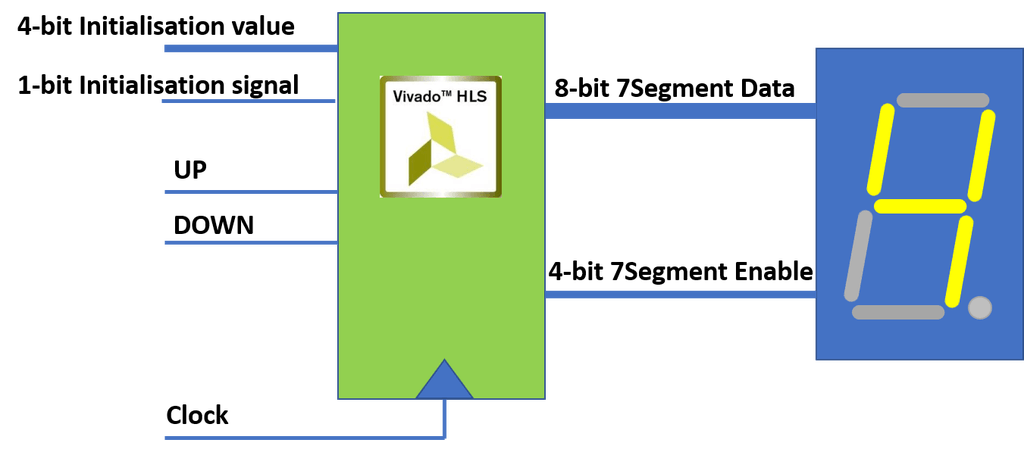

项目描述:在这个项目中,我将设计一个带有初始化信号的 0-9 加/减计数器。图 1 显示了该项目的概览。

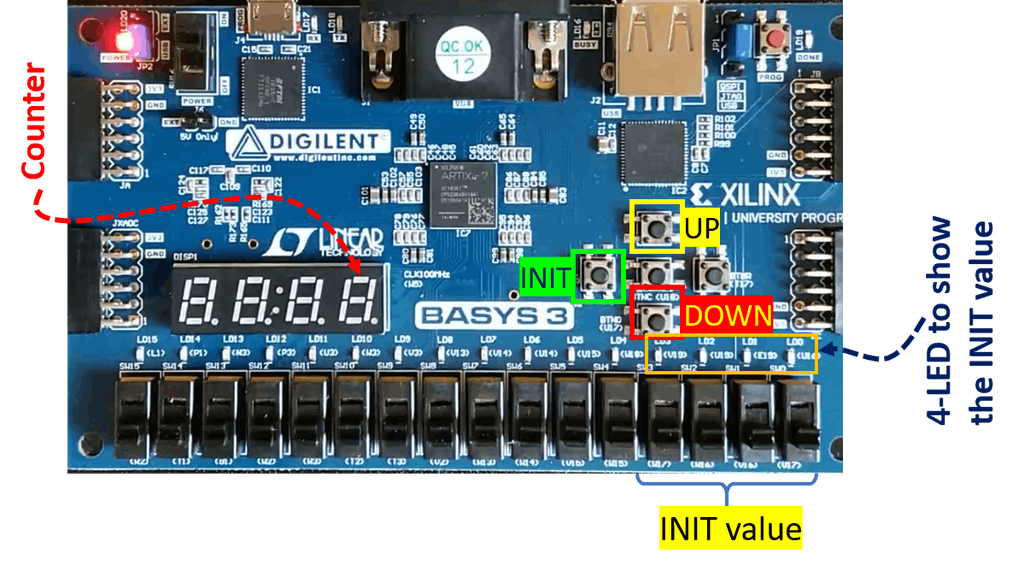

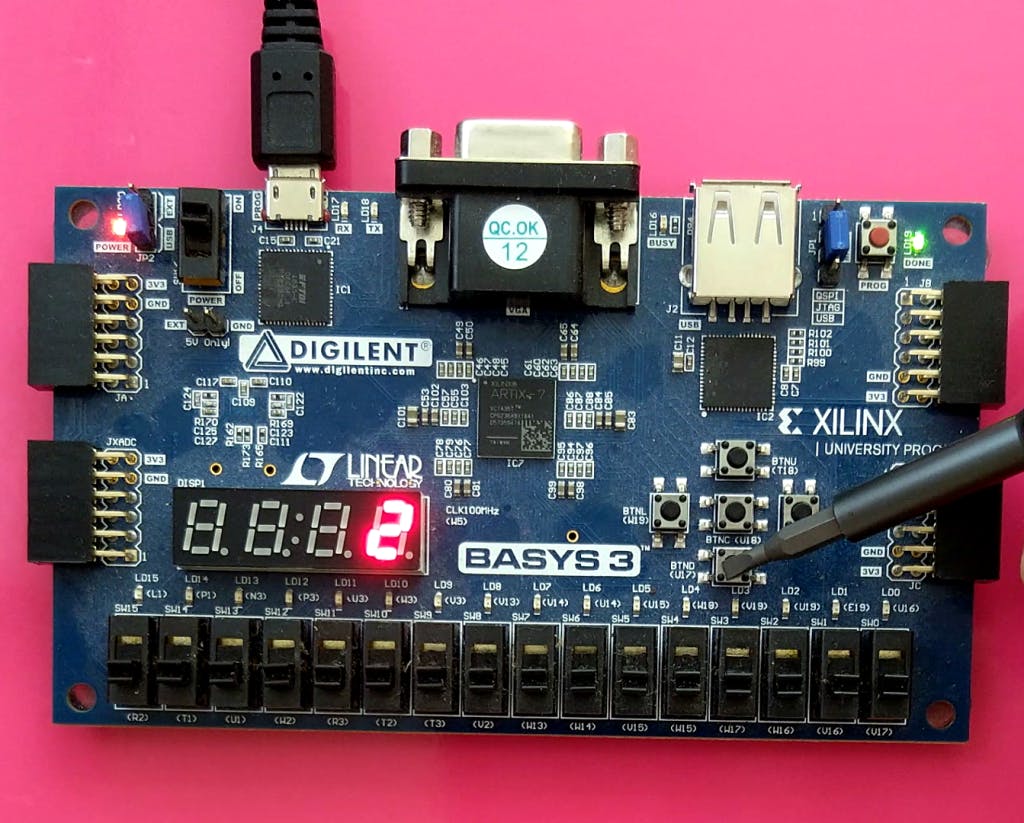

为了实现这个项目,我使用了 Vivado Design Suite – HLx Editions 提供的 Xilinx HLS 平台。此外,我将使用 Basys 3 评估板作为目标 FPGA 平台。图 2 显示了板上最终递增/递减计数器的布局。右侧的 7 段显示计数器。UP 按钮用于向上计数,DOWN 按钮用于向下计数。INIT 按钮初始化计数器。用“INIT value”表示的四个滑动开关用于输入初始化编号。此外,四个 LED 显示该值。

我们分三个阶段来实施这个项目:C/C++ 描述、逻辑综合和电路板编程。

第 1 阶段:C/C++ 描述(Vivado-HLS 项目)

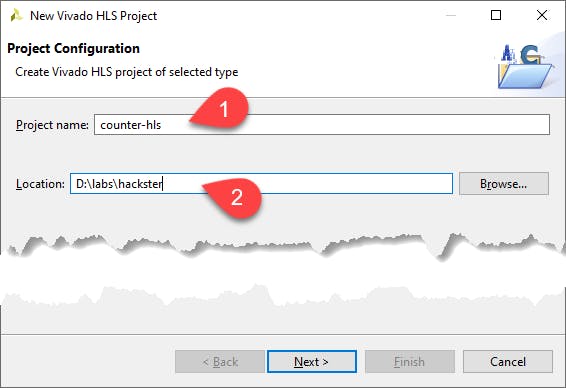

1- 运行 Vivado-HLS IDE 并创建一个新项目。

2- 在创建新项目向导的第一页中,插入“counter-vhls”作为项目名称,并为项目文件选择适当的位置。

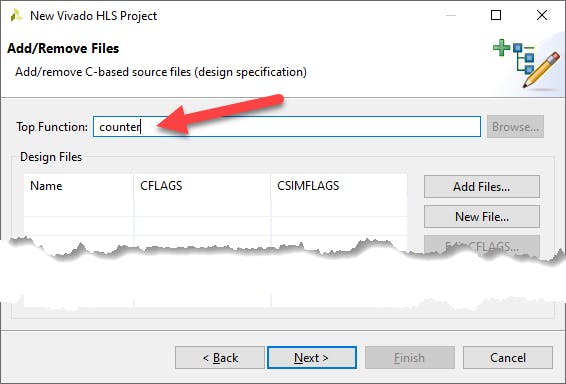

3-选择“计数器”作为顶级功能名称。

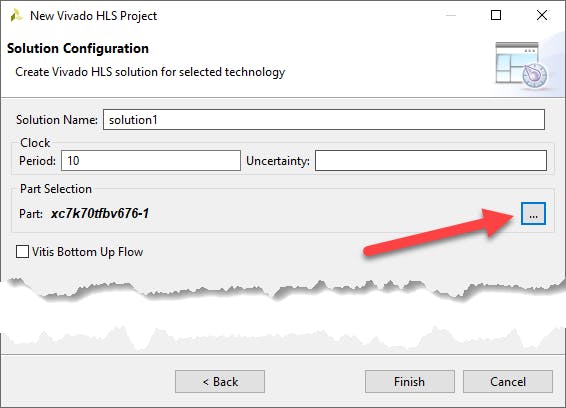

4- 在“解决方案配置”页面中,单击省略号按钮选择 FPGA 平台。

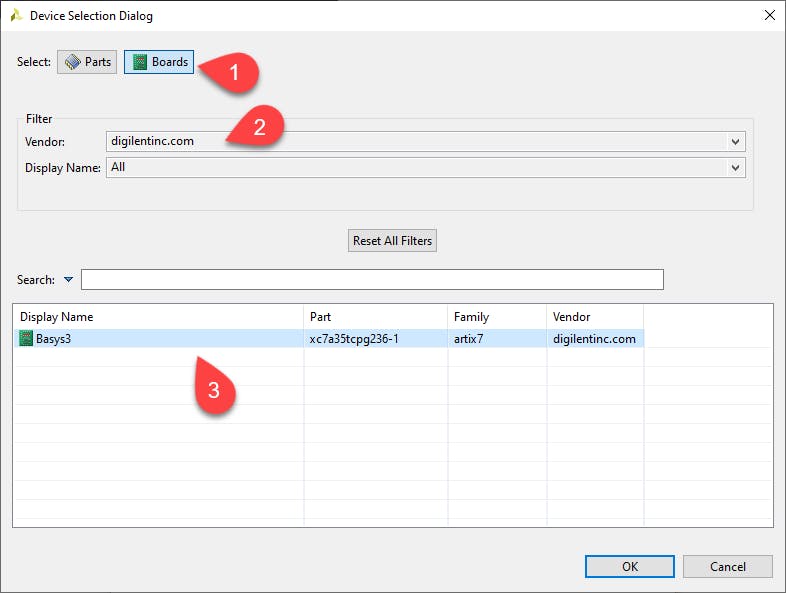

5- 设备选择对话框将打开。点击Boards,找到digilent vendor,选择Basys3 board,点击OK。

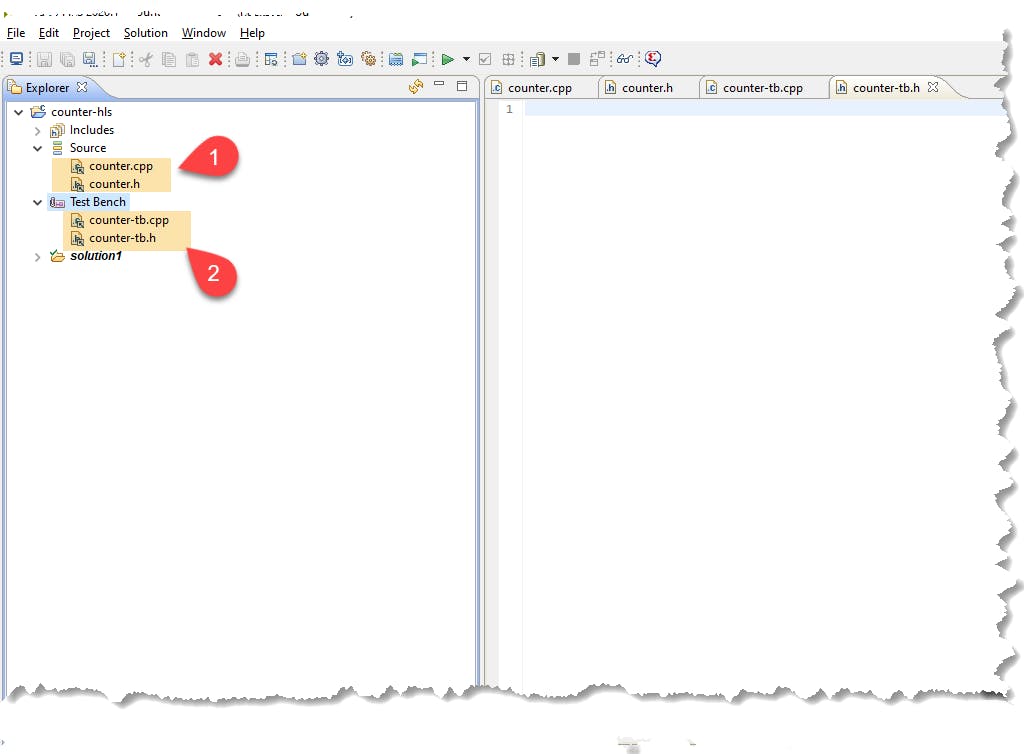

6- 在 Source 文件夹下创建两个名为“counter.cpp”和“counter.h”的新文件。

7- 在 Test Bench 文件夹下创建两个名为“counter-tb.cpp”和“counter-tb.h”的新文件。

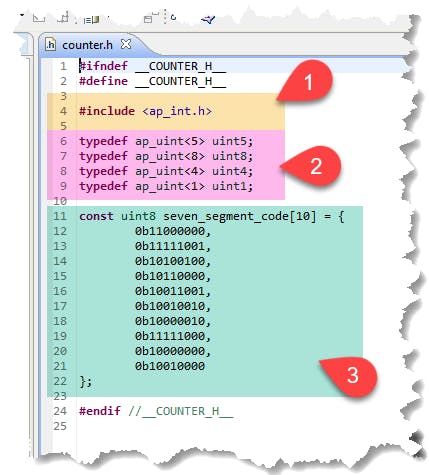

8-让我们编写设计头文件如下。如下图所示,该文件中的代码分为三个部分:

1- 首先,由于我们要使用 HLS 任意精度数据类型,我们应该包含“ap_int.h”头文件。2- 其次,我们定义了一些稍后在设计中使用的数据类型 3- 最后,我们定义了一个常量数组,用于保存对应于从 0 到 9 的数字的 7 段代码。

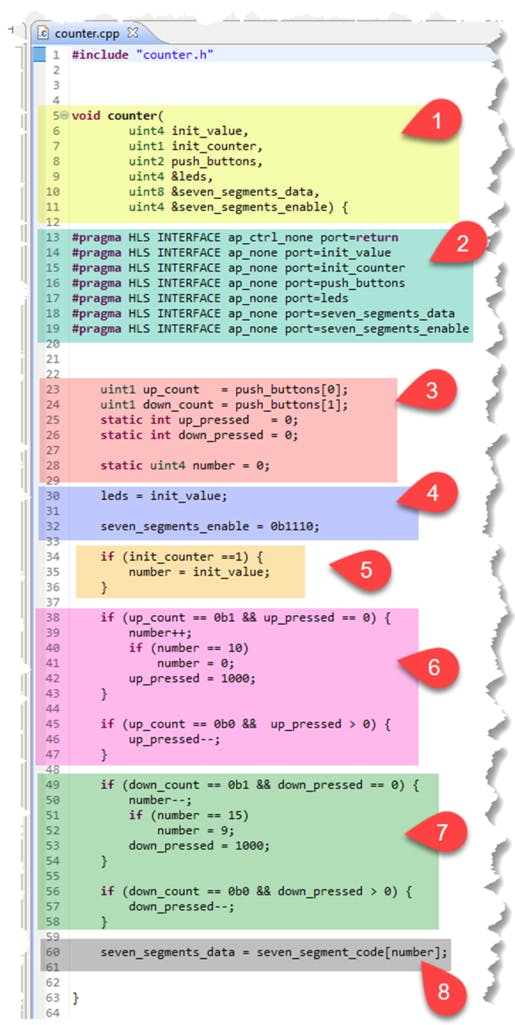

9- 设计源文件包含顶层功能描述。它由八个部分组成。

1-顶级函数参数:该函数包含三个输入和两个输出参数。

init_value变量包含计数器初始值。

reset_counter变量确定何时应该初始化计数器。当它为 1 时,计数器获取init_value参数中的值。

push_buttons变量确定向上或向下计数。

Seven_segments_data变量包含对应于计数器状态的 7 段代码

Seven_segments_enable变量启用目标 7 段。

2-端口接口:本节定义与顶级函数参数对应的端口接口。这些接口定义了实现参数数据事务的硬件结构。由于我们有一个简单的设计,并且我们希望简单的电线实现参数,我选择了ap_none作为接口模式。

3-声明变量:在这里,我声明了一些要在设计中使用的变量。如果按下 UP 按钮,up_count 变量将为1 。如果按下 DOWN 按钮,则 down_count 将为1 。up_pressed和down_pressed被声明为静态变量以保存按钮的历史记录。number变量保持计数器状态,因此定义为静态变量。

4-设置输出:此部分将 INIT 值发送到 LED 并启用右侧 7 段。

5-初始化:如果reset_counter信号被激活,这个if 语句初始化计数器状态。

6-向上计数:这部分由两个if 语句组成。第一个检查是否按下了向上按钮。第二个if检查 UP 按钮是否已被释放。

7-向下计数:这部分与向上计数部分非常相似。

8- 7 段码:最后一段发出计数器状态对应的 7 段码。

10- 现在,我们需要一个 C/C++ 测试平台来测试设计。可以在此处找到测试台文件。测试台分为三个步骤:

— 生成测试向量, — 将测试向量应用于设计, — 最后,将硬件输出与黄金模型的输出进行比较并报告任何差异

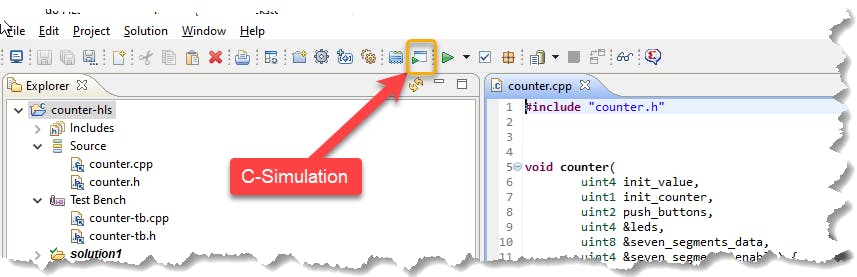

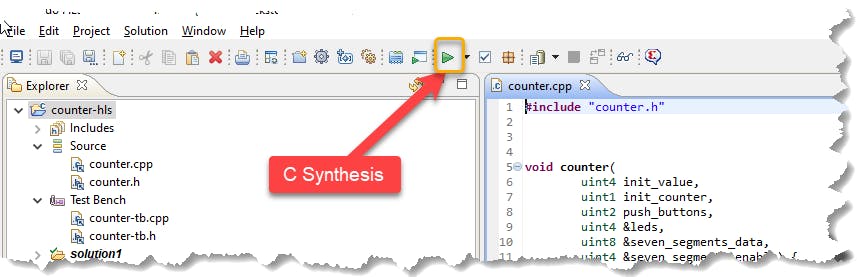

11- 现在我们可以通过单击工具栏中的图标来运行 C 模拟。

12-成功完成C-Simulation后,我们可以运行高级综合。

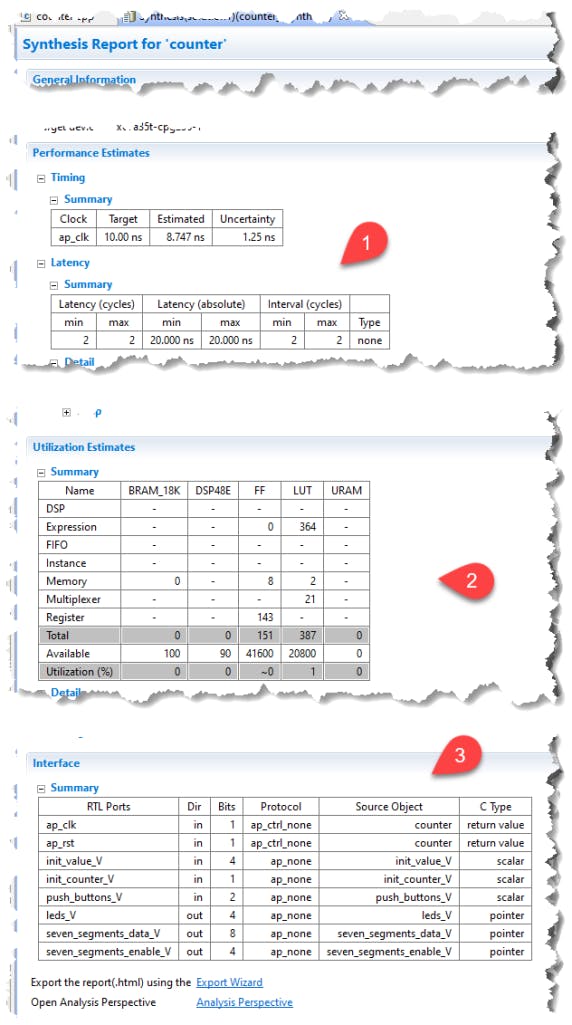

图 13 显示了综合报告的部分内容。它有三个主要部分:

1- 时序信息 2- 资源利用 3- 端口接口

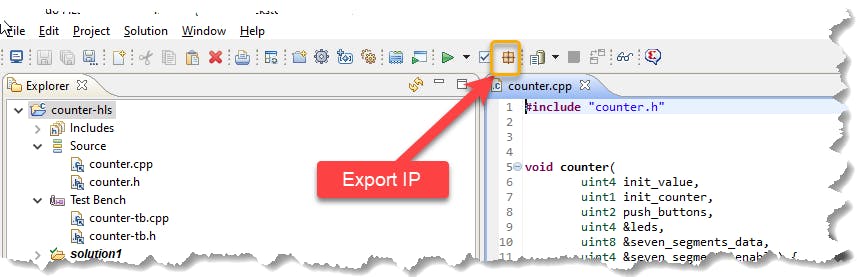

13- 最后,我们应该通过单击其图标来生成和导出设计 RTL-IP。

第 2 阶段:逻辑综合(Vivado 项目)

现在,我们已准备好进行逻辑综合和生成 FPGA 比特流。

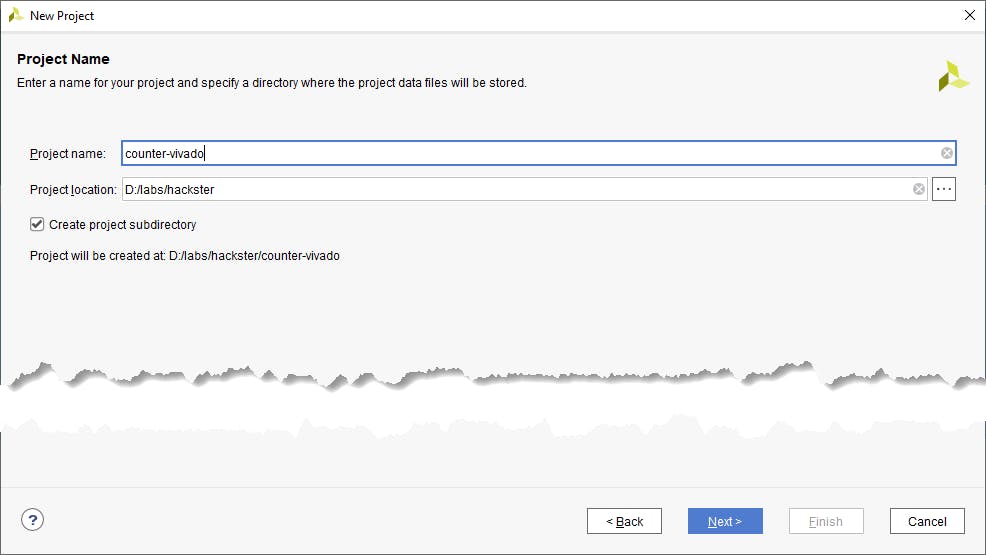

1-创建一个名为counter-vivado的新Vivado项目。请注意,该项目没有任何源文件。

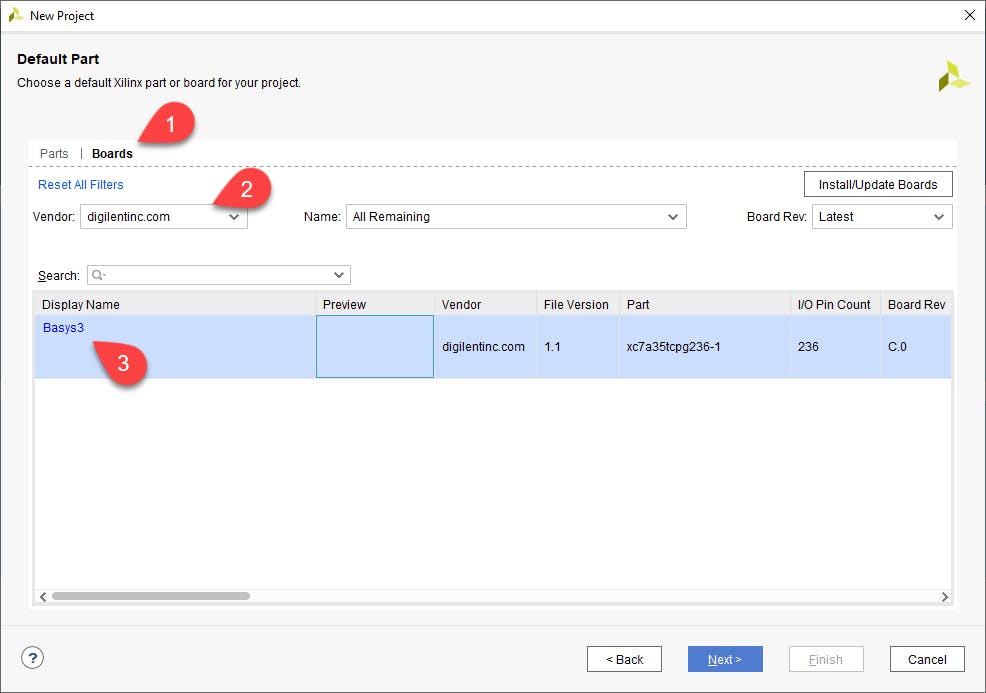

2- 不要忘记选择 Basys-3 板作为目标 FPGA。

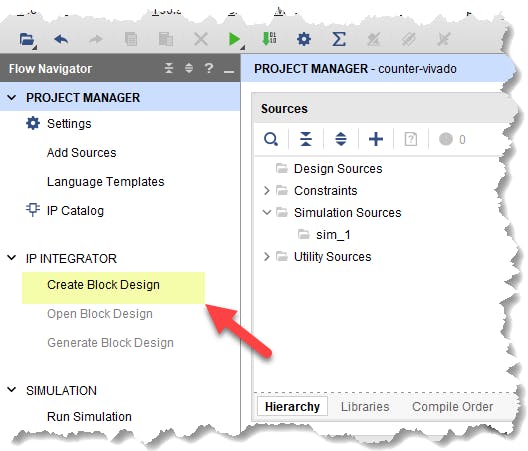

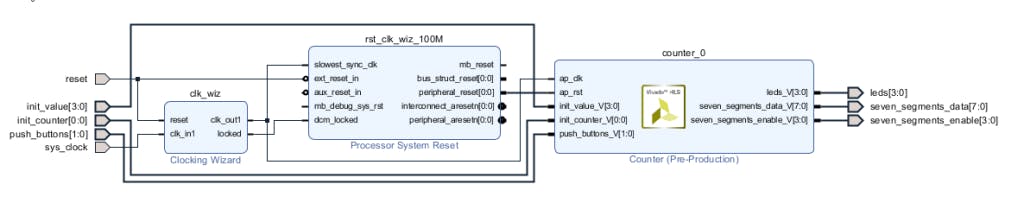

3-创建一个新的块设计

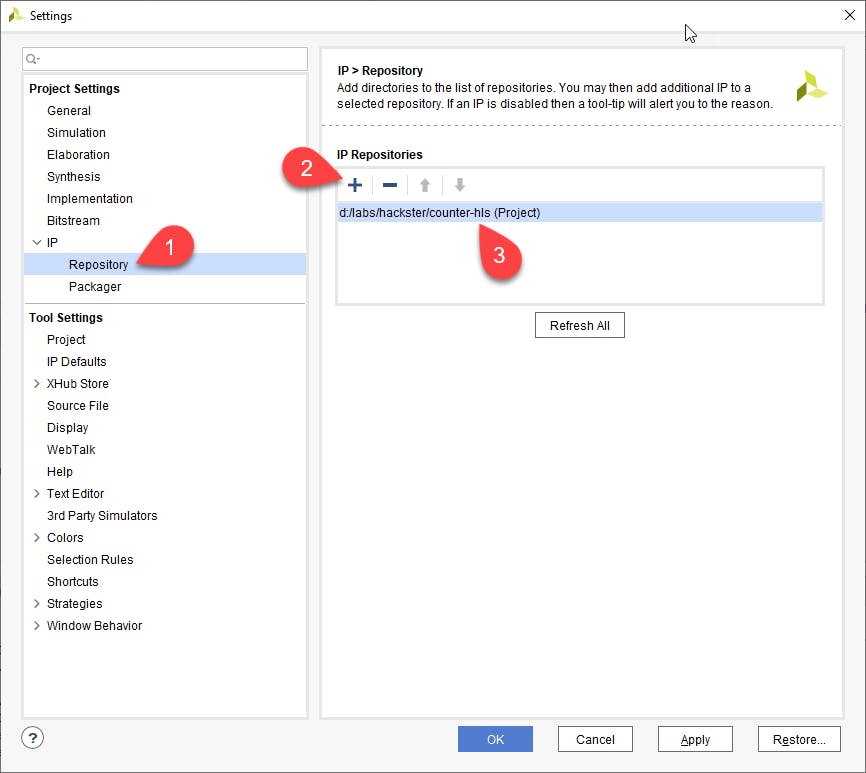

4-右键单击图表区域内的某处并选择“IP设置...”选项

5-然后单击设置对话框中IP下的存储库选项。然后点击右侧的加号,浏览到counter HLS项目文件夹。Vivado 在文件夹中搜索任何可能的 IP 并将其添加到其存储库中。

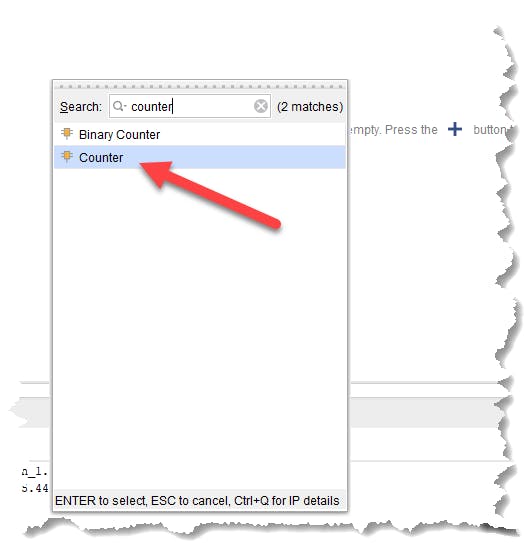

6- 右键单击图表区域内的某处并选择“添加..”选项。然后搜索计数器 IP 并将其添加到 vivado 项目中。

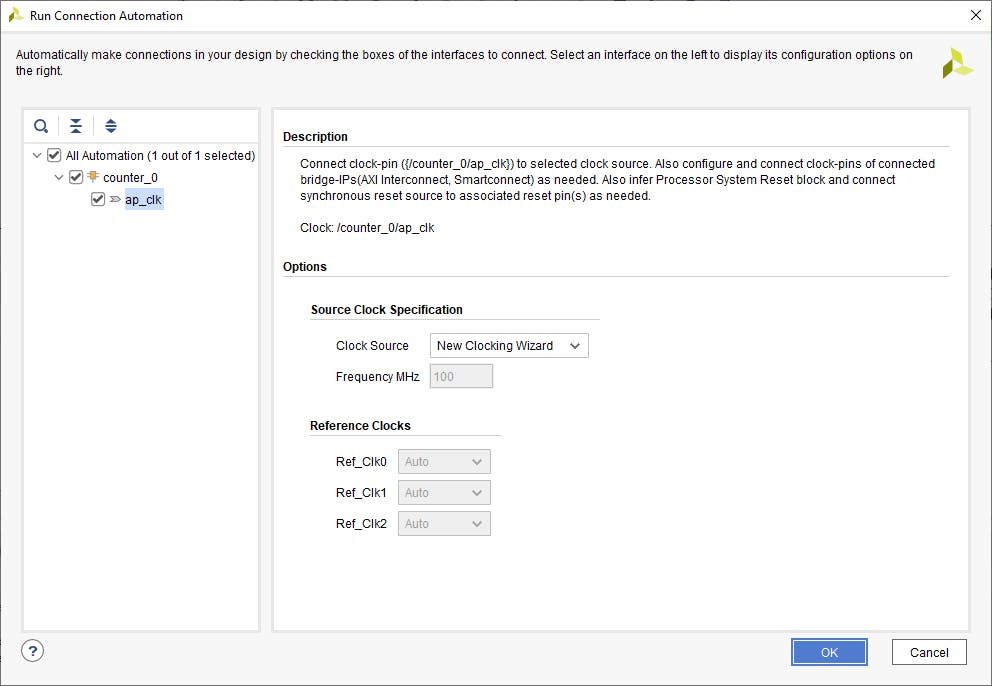

17- 单击图表区域顶部的“运行连接自动化”。

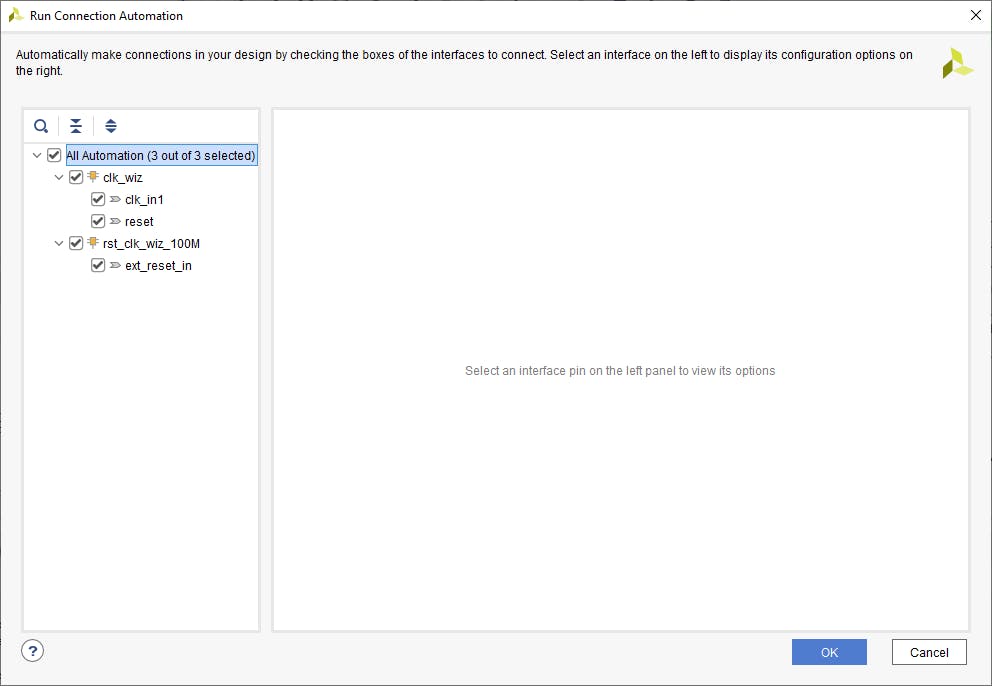

18- 再次单击图表区域顶部的“运行连接自动化”。

9- 在我们的计数器 IP 上选择未连接的端口并将它们设为外部(右键单击端口名称,您将在下拉菜单中看到“设为外部”选项)。

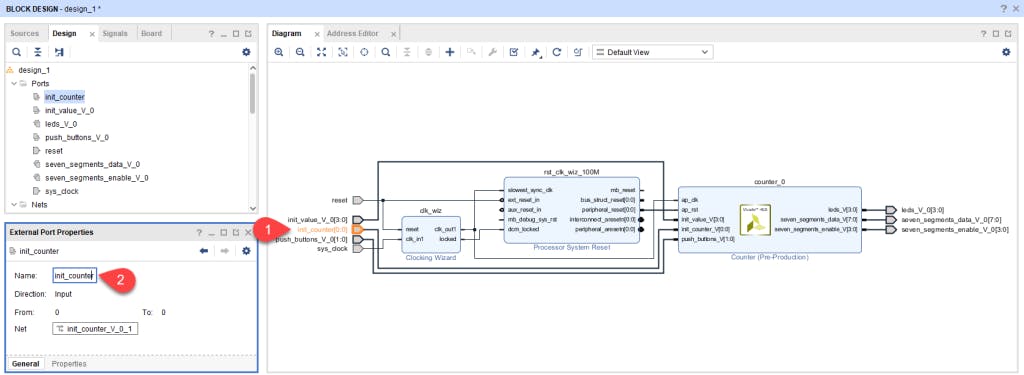

10-您可以通过选择端口并使用“外部端口属性”窗口来重命名端口。

init_counter_V_0 -----------> init_counter

push_buttons_V_0------------> push_buttons

init_value_V_0--------------> init_value

init_counter----------------> init_counter

leds_V_0--------------------> leds

seven_segments_data_V_0 ----> seven_segments_data

seven_segments_enable_V_0---> seven_segments_enable

11- 现在创建一个约束文件,并添加以下约束以将 IP 端口连接到具有适当 I/O 标准的 FPGA 引脚。

## Switches

set_property PACKAGE_PIN V17 [get_ports {init_value[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[0]}]

set_property PACKAGE_PIN V16 [get_ports {init_value[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[1]}]

set_property PACKAGE_PIN W16 [get_ports {init_value[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[2]}]

set_property PACKAGE_PIN W17 [get_ports {init_value[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {init_value[3]}]

# LEDs

set_property PACKAGE_PIN U16 [get_ports {leds[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[0]}]

set_property PACKAGE_PIN E19 [get_ports {leds[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[1]}]

set_property PACKAGE_PIN U19 [get_ports {leds[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[2]}]

set_property PACKAGE_PIN V19 [get_ports {leds[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[3]}]

#7 segment display

set_property PACKAGE_PIN W7 [get_ports {seven_segments_data[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[0]}]

set_property PACKAGE_PIN W6 [get_ports {seven_segments_data[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[1]}]

set_property PACKAGE_PIN U8 [get_ports {seven_segments_data[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[2]}]

set_property PACKAGE_PIN V8 [get_ports {seven_segments_data[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[3]}]

set_property PACKAGE_PIN U5 [get_ports {seven_segments_data[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[4]}]

set_property PACKAGE_PIN V5 [get_ports {seven_segments_data[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[5]}]

set_property PACKAGE_PIN U7 [get_ports {seven_segments_data[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_data[6]}]

set_property PACKAGE_PIN V7 [get_ports seven_segments_data[7]]

set_property IOSTANDARD LVCMOS33 [get_ports seven_segments_data[7]]

set_property PACKAGE_PIN U2 [get_ports {seven_segments_enable[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[0]}]

set_property PACKAGE_PIN U4 [get_ports {seven_segments_enable[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[1]}]

set_property PACKAGE_PIN V4 [get_ports {seven_segments_enable[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[2]}]

set_property PACKAGE_PIN W4 [get_ports {seven_segments_enable[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segments_enable[3]}]

#Buttons

set_property PACKAGE_PIN T18 [get_ports push_buttons[0]]

set_property IOSTANDARD LVCMOS33 [get_ports push_buttons[0]]

set_property PACKAGE_PIN W19 [get_ports init_counter[0]]

set_property IOSTANDARD LVCMOS33 [get_ports init_counter[0]]

set_property PACKAGE_PIN U17 [get_ports push_buttons[1]]

set_property IOSTANDARD LVCMOS33 [get_ports push_buttons[1]]

12- 现在右键单击图表区域内的某处并选择“验证设计”选项。

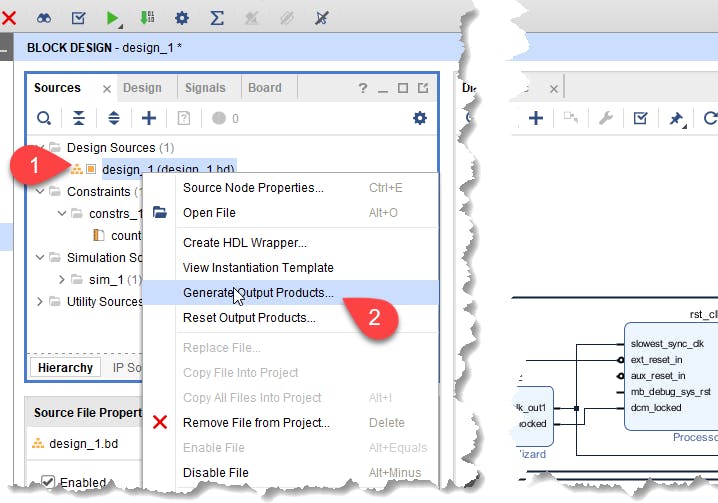

13-成功验证设计后,右键单击“Design Sources”文件夹下的“ design_1 ”并选择“Generate Output Products...”

14- 然后,再次右键单击“Design Sources”文件夹下的“design_1”并选择“Create HDL Wrapper...”

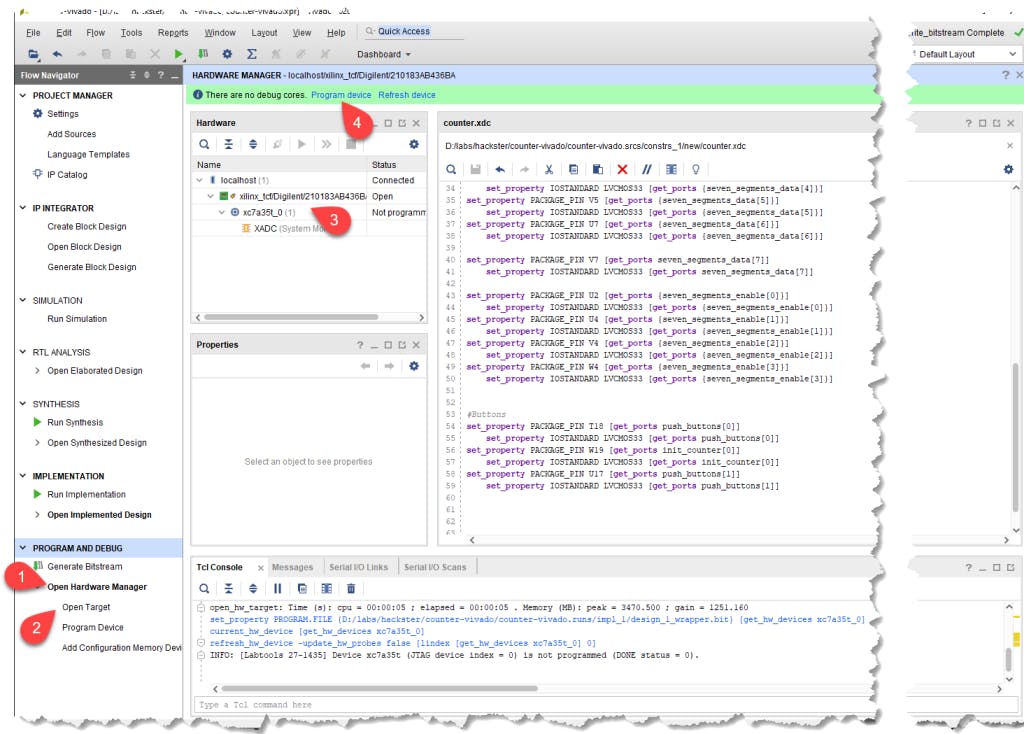

15- 现在单击左侧 Flow Navigator 中 PROGRAM and DEBUG 下的“Generate Bitstream”选项。

第 3 阶段:电路板编程

1- 最后,对电路板进行编程并检查设计。

如果您对使用 HLS 进行设计感兴趣,请查看具有FPGA 高级合成的数字系统设计:组合电路

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章