资料下载

×

数据表:1.8 v / 2.5 v / 3.3 v,LVCMOS峰值减少EMI时钟发生器

消耗积分:0 |

格式:rar |

大小:0.04 MB |

2017-04-06

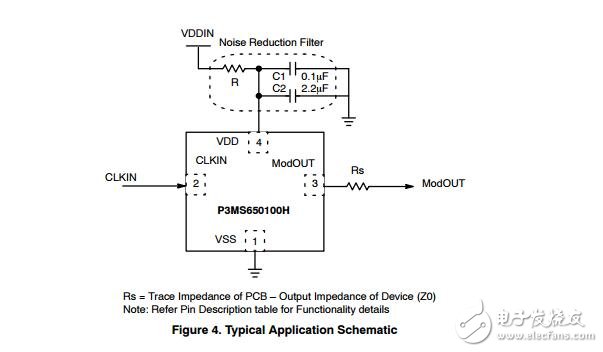

P3MS650100H→断电模式节省电能CLKIN销没有时钟。 ModOUT在掉电模式下“低”。

P3MS650100H运作超过-20°C + 85°C和有一个4针WDFN(1.2 mmx1.0mm)包。

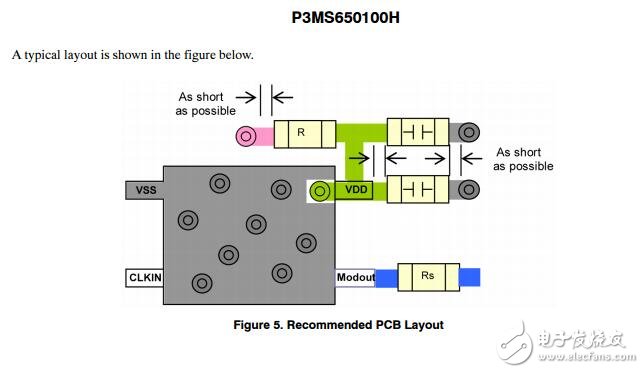

为了获得最佳的设备性能,以下准则建议。

♦专用VDD和GND平面。

♦装置必须从系统电源噪声隔离。间接一只0.1F和一个2.2μF的去耦电容

安装在尽可能靠近VDD引脚的董事会的组成部分方面。之间无需使用通孔

去耦电容和VDD引脚。PCB跟踪到VDD引脚和地面通过应尽可能短

可能的。所有的VDD引脚应具有去耦电容。

♦在最佳布局的所有组件都在同一侧的板,减少通过其他信号层孔。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章