资料下载

集成锁相环提供更高的频率性能,提高用户的利益

集成锁相环提供更高的频率性能,提高用户的利益

锁相环(PLL)是电子系统中最通用,灵活和有价值的电路配置之一,导致其在许多应用中的应用。它是用于时钟同步和恢复,作为频率合成器,并作为一个可调谐振荡器,仅举几个例子。其结果是,PLL被发现在许多射频设备项目,包括无线电接收机和测试设备。根据其具体实施,它可以从近DC到GHz和更高的频率,实现了系统和电路中的许多关键角色。

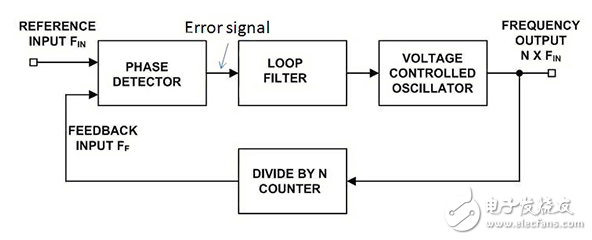

PLL是一个闭环(负反馈)架构,基本锁相环由这些块组成(图1):

Figure 1: A basic PLL is a closed-loop, negative feedback system where the error between a reference signal and the VCO output is used to correct that output; the low-pass filter is a critical element in establishing the loop’s dynamics.

A phase/frequency detector (PFD) (often simply called a phase-detector PD) compares an input signal to a reference signal and produces an error signal which is proportional to their phase difference (keep in mind that phase and frequency are intimately related, as frequency is the time derivative of phase); the phase-detector output usually goes to a charge pump which transforms the small current difference into a larger voltage

A low-pass filter (LPF), which shapes the spectrum of the error signal; the design of this filter is often a combination of engineering science and intuitive art, and is a major factor in setting many of the dynamics of PLL operation

A voltage-controlled oscillator (VCO) with output phase/frequency controlled by the error signal

An optional frequency divider at the VCO output, which causes the PLL to generate frequencies at a multiple factor N of the reference frequency; N can be an integer, and many PLL designs support fractional-N non-integer division

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章