资料下载

使用智能外设提高CPU效率

使用智能外设提高CPU效率

现代微控制器添加了一个范围广泛的新功能,在正确使用时可以大大提高应用效率。特别是,可以使用独立于CPU独立操作的智能外设和外围设备,允许CPU并行执行其他任务,或者进入低功耗睡眠模式。使用这两种技术都将提高整体处理效率和节约能源。

DMA控制器

在基于MCU的设计中遇到的第一个智能外设之一是直接存储器存取(DMA)控制器。这个专用硬件块可以在内存和/或外设之间传输数据,而不需要CPU与每个传输相关。先进的DMA控制器,如包括对意法半导体STM32F4的家庭,可以进一步减少CPU的使用功能灵活的数据流分配和转移管理。让我们更详细地看看其中的一些特性,看看它们如何被用来提高处理效率。

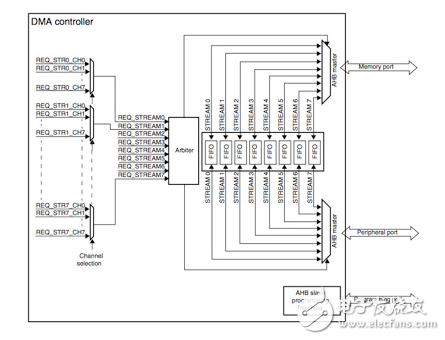

Figure 1 shows a block diagram representing the variety of data paths available in one of the two DMA controllers on STM32F4 devices. As shown on the left side of the figure, DMA requests originate from eight different channels (allocated to the various DMA-enabled peripherals) and are routed to eight different request inputs on the arbiter, establishing a priority (lower-numbered inputs have higher priority)。 The highest-priority transfer is then activated, and the AHB Masters, on the right side of the figure, execute the desired data transfer. Separate masters for both the memory and the peripheral interfaces further improve efficiency for peripheral-to-memory transfers, probably the most prevalent use of a DMA in MCU-based designs.

The allocation of separate FIFOs for each stream, as shown in the middle of Figure 1, allows the FIFO characteristics to be tuned for each peripheral interface’s characteristics. For example, the threshold level of the FIFO (depth at which a transfer is requested) can be individually set at ¼, ½, or ¾ of the FIFO size. This allows lower-speed channels to wait until the FIFO is almost full before a transfer to minimize overhead. Faster channels would initiate a transfer sooner, perhaps at ½ the size to avoid a FIFO overrun.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章