资料下载

×

基于Altera在65nm半导体工艺上的技术和方法

消耗积分:0 |

格式:rar |

大小:0.19 MB |

2017-09-04

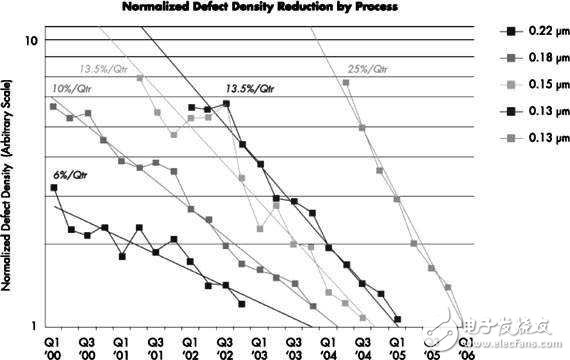

Altera在65nm半导体制造工艺上的发展策略是充分利用先进的技术和方法,以最低的成本为客户提供性能最好的器件,同时降低客户风险,保证产品尽快面市。Altera在130nm和90nm器件上的市场份额表明,有效控制高端半导体技术中存在的风险,能够提高FPGA体系结构在市场上的受欢迎程度。因此,早自2003年初以来,Altera就一直在稳步开发和测试其65nm技术。本文研究Altera在65nm工艺上的工程策略,介绍公司如何为客户降低生产和计划风险,并同时从根本上提高密度、性能,及降低成本和功耗。随着半导体制造技术达到新的极限,在65nm工艺节点上出现了特殊的产品规划、设计和交付挑战。在130nm和90nm通道尺度上还可以处理的深亚微米效应,包括功耗增加、工艺偏差以及参数失效等,成为65nm工艺最显著的工程挑战。这一工艺节点的IC开发存在很大的风险,会影响FPGA的工艺和性能。由于许多客户选择了可编程逻辑作为减小风险的策略,Altera应用业界最前沿、最全面的方法来控制这种风险。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章