资料下载

×

HyperLink编程的额外信息补充

消耗积分:1 |

格式:rar |

大小:0.9 MB |

2017-10-17

摘要

HyperLink为两个KeyStone架构DSP之间提供了一种高速,低延迟,引脚数量少的通信接口。HyperLink的用户手册已经详细的对其进行了描述。本文主要是为HyperLink的编程提供了一些额外的补充信息。

同时本文还讨论了HyperLink的性能,提供了在各种操作条件下的性能测试数据。对影响HyperLink性能的一些参数进行了讨论。

文章的最后附上对应本文的应用代码。

1、HyperLink介绍

HyperLink为两片DSP之间提供一种高速、低延迟,引脚数少的通信连接接口。

HyperLink的设计速度最高速率支持12.5Gbps,目前在大部分的KeyStone DSPs上,由于受限于SerDes和板级布线,速度接近为10Gbps.HyperLink是TI专有的外设接口。相对于用于高速Serdes接口的传统的8b10b编码方式,HyperLink减少了编码冗余,编码方式等效于8b9b.单片DSP为HyperLink提供4个SerDes通道,所以10Gbps的HyperLink理论吞吐率为10*4*(8/9)= 35.5Gbps= 4.44GB/s.

HyperLink使用了PCIE类似的内存映射机制,但它为多核DSP提供了一些更灵活的特性。本文将会使用几个范例来详细解释这一点。

本文还讨论了HyperLink的性能,提供了在各种操作条件下的性能测试数据。对影响HyperLink性能的一些因素进行了讨论。

2、HyperLink配置

本节提供了一些配置HyperLink模块的补充信息。

2.1 Serdes配置

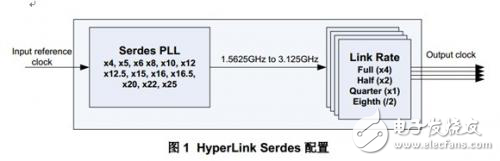

Serdes必须配置成期望的链接速度。图1表示了输入参考时钟和输出时钟之间的关系。

输入参考时钟建议限制在156.25MHz ~312.5MHz范围内。Serdes PLL的倍频系数必须合理配置生成的内部时钟(internal clock)限制在1.5625GHz ~ 3.125GHz范围内。

最后的链接速度由内部时钟(internal clock)驱动,通过link rate配置来得到。

2.2 HyperLink存储映射配置

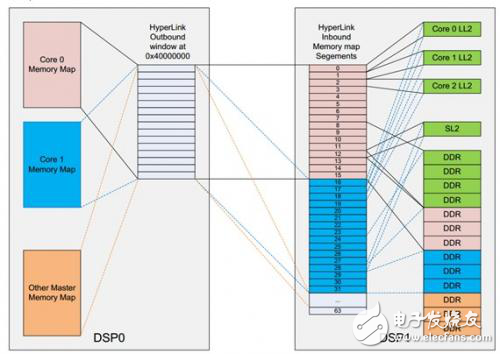

HyperLink的存储映射非常的灵活。HyperLink的用户手册对此作了详细的描述。本节将用两个例子来详细的解释它。图2是第一个例子。

图2通过HyperLink窗口映射到远端不同类型的存储空间

在这个例子里面,DSP1的存储空间映射到了DSP0的存储空间窗口0x40000000~0x50000000DSP0可以访问DSP1的所有内存空间,包括LL2,SL2,DDR,就像访问自己的本地的存储空间一样。在DSP0上,所有的Master都可以通过以0x40000000起始的Outbound窗口地址来访问DSP1的存储空间,但是不同master事实上可能访问到DSP1上不同的存储空间。原因是HyperLink发送侧传输数据时,会将PrivID一起传输。接受侧通过PrivID值,可以建立不同的地址映射表

HyperLink为两个KeyStone架构DSP之间提供了一种高速,低延迟,引脚数量少的通信接口。HyperLink的用户手册已经详细的对其进行了描述。本文主要是为HyperLink的编程提供了一些额外的补充信息。

同时本文还讨论了HyperLink的性能,提供了在各种操作条件下的性能测试数据。对影响HyperLink性能的一些参数进行了讨论。

文章的最后附上对应本文的应用代码。

1、HyperLink介绍

HyperLink为两片DSP之间提供一种高速、低延迟,引脚数少的通信连接接口。

HyperLink的设计速度最高速率支持12.5Gbps,目前在大部分的KeyStone DSPs上,由于受限于SerDes和板级布线,速度接近为10Gbps.HyperLink是TI专有的外设接口。相对于用于高速Serdes接口的传统的8b10b编码方式,HyperLink减少了编码冗余,编码方式等效于8b9b.单片DSP为HyperLink提供4个SerDes通道,所以10Gbps的HyperLink理论吞吐率为10*4*(8/9)= 35.5Gbps= 4.44GB/s.

HyperLink使用了PCIE类似的内存映射机制,但它为多核DSP提供了一些更灵活的特性。本文将会使用几个范例来详细解释这一点。

本文还讨论了HyperLink的性能,提供了在各种操作条件下的性能测试数据。对影响HyperLink性能的一些因素进行了讨论。

2、HyperLink配置

本节提供了一些配置HyperLink模块的补充信息。

2.1 Serdes配置

Serdes必须配置成期望的链接速度。图1表示了输入参考时钟和输出时钟之间的关系。

输入参考时钟建议限制在156.25MHz ~312.5MHz范围内。Serdes PLL的倍频系数必须合理配置生成的内部时钟(internal clock)限制在1.5625GHz ~ 3.125GHz范围内。

最后的链接速度由内部时钟(internal clock)驱动,通过link rate配置来得到。

2.2 HyperLink存储映射配置

HyperLink的存储映射非常的灵活。HyperLink的用户手册对此作了详细的描述。本节将用两个例子来详细的解释它。图2是第一个例子。

图2通过HyperLink窗口映射到远端不同类型的存储空间

在这个例子里面,DSP1的存储空间映射到了DSP0的存储空间窗口0x40000000~0x50000000DSP0可以访问DSP1的所有内存空间,包括LL2,SL2,DDR,就像访问自己的本地的存储空间一样。在DSP0上,所有的Master都可以通过以0x40000000起始的Outbound窗口地址来访问DSP1的存储空间,但是不同master事实上可能访问到DSP1上不同的存储空间。原因是HyperLink发送侧传输数据时,会将PrivID一起传输。接受侧通过PrivID值,可以建立不同的地址映射表

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章