资料下载

×

ARM微处理器编程模型之异常中断处理分析

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-10-18

3.4 异常中断处理

异常或中断是用户程序中最基本的一种执行流程和形态。这部分主要对ARM架构下的异常中断做详细说明。

ARM有7种类型的异常,按优先级从高到低的排列如下:复位异常(Reset)、数据异常(Data Abort)、快速中断异常(FIQ)、外部中断异常(IRQ)、预取异常(Prefetch Abort)、软件中断(SWI)和未定义指令异常(Undefined instruction)。

注意在ARM文档中,使用术语Exception来描述异常。Exception主要是从处理器被动接受异常的角度出发,而Interrupt带有向处理器主动申请的色彩。在本书中,对“异常”和“中断”不做严格区分,两者都是指请求处理器打断正常的程序执行流程,进入特定程序循环的一种机制。

注意在ARM文档中,使用术语Exception来描述异常。Exception主要是从处理器被动接受异常的角度出发,而Interrupt带有向处理器主动申请的色彩。在本书中,对“异常”和“中断”不做严格区分,两者都是指请求处理器打断正常的程序执行流程,进入特定程序循环的一种机制。

3.4.1 异常种类

ARM体系结构中,存在7种异常处理。当异常发生时,处理器会把PC设置为一个特定的存储器地址。这一地址放在被称为向量表(vector table)的特定地址范围内。向量表的入口是一些跳转指令,跳转到专门处理某个异常或中断的子程序。

存储器映射地址0x00000000是为向量表(一组32位字)保留的。在有些处理器中,向量表可以选择定位在存储空间的高地址(从偏移量0xffff0000开始)。一些嵌入式操作系统,如Linux和Windows CE就要利用这一特性。

表3.4列出了ARM的7种异常。

表3.4 ARM的7种异常

异 常 类 型处理器模式执行低地址执行高地址

复位异常(Reset)特权模式0x000000000xFFFF0000

未定义指令异常(Undefined interrupt)未定义指令中止模式0x000000040xFFFF0004

软中断异常(Software Abort)特权模式0x000000080xFFFF0008

预取异常(Prefetch Abort)数据访问中止模式0x0000000C0xFFFF000C

数据异常(Data Abort)数据访问中止模式0x000000100xFFFF0010

外部中断请求IRQ外部中断请求模式0x000000180xFFFF0018

快速中断请求FIQ快速中断请求模式0x0000001C0xFFFF001C

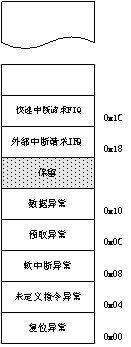

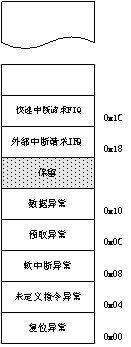

异常处理向量表如图3.5所示。

当异常发生时,分组寄存器r14和SPSR用于保存处理器状态,操作伪指令如下。

R14_《exception_mode》 = return link

SPSR_《exception_mode》 = CPSR

CPSR[4∶0] = exception mode number

CPSR[5] = 0 /*进入ARM状态*/

If 《exception_mode》 = = reset or FIQ then

CPSR[6] = 1 /*屏蔽快速中断FIQ*/

CPSR[7] = 1 /*屏蔽外部中断IRQ*/

PC = exception vector address

图3.5 异常处理向量表

异常返回时,SPSR内容恢复到CPSR,连接寄存器r14的内容恢复到程序计数器PC。

1.复位异常

当处理器的复位引脚有效时,系统产生复位异常中断,程序跳转到复位异常中断处理程序处执行。复位异常中断通常用在下面两种情况下。

· 系统上电。

· 系统复位。

当复位异常时,系统执行下列伪操作。

R14_svc = UNPREDICTABLE value

SPSR_svc = UNPREDICTABLE value

CPSR[4∶0] = 0b10011 /*进入特权模式*/

CPSR[5] = 0 /*处理器进入ARM状态*/

CPSR[6] = 1 /*禁止快速中断*/

CPSR[7] = 1 /*禁止外设中断*/

If high vectors configured then

PC = 0xffff0000

Else

PC = 0x00000000

复位异常中断处理程序将进行一些初始化工作,内容与具体系统相关。下面是复位异常中断处理程序的主要功能。

· 设置异常中断向量表。

· 初始化数据栈和寄存器。

· 初始化存储系统,如系统中的MMU等。

· 初始化关键的I/O设备。

· 使能中断。

· 处理器切换到合适的模式。

· 初始化C变量,跳转到应用程序执行。

2.未定义指令异常

当ARM处理器执行协处理器指令时,它必须等待一个外部协处理器应答后,才能真正执行这条指令。若协处理器没有相应,则发生未定义指令异常。

未定义指令异常可用于在没有物理协处理器的系统上,对协处理器进行软件仿真,或通过软件仿真实现指令集扩展。例如,在一个不包含浮点运算的系统中,CPU遇到浮点运算指令时,将发生未定义指令异常中断,在该未定义指令异常中断的处理程序中可以通过其他指令序列仿真浮点运算指令。

仿真功能可以通过下面步骤实现。

① 将仿真程序入口地址链接到向量表中未定义指令异常中断入口处(0x00000004或0xffff0004),并保存原来的中断处理程序。

② 读取该未定义指令的bits[27∶24],判断其是否是一条协处理器指令。如果bits[27∶24]值为0b1110或0b110x,该指令是一条协处理器指令;否则,由软件仿真实现协处理器功能,可以同过bits[11∶8]来判断要仿真的协处理器功能(类似于SWI异常实现机制)。

③ 如果不仿真该未定义指令,程序跳转到原来的未定义指令异常中断的中断处理程序执行。

当未定义异常发生时,系统执行下列的伪操作。

r14_und = address of next instruction after the undefined instruction

SPSR_und = CPSR

CPSR[4∶0] = 0b11011 /*进入未定义指令模式*/

CPSR[5] = 0 /*处理器进入ARM状态*/

/*CPSR[6]保持不变*/

CPSR[7] = 1 /*禁止外设中断*/

If high vectors configured then

PC = 0xffff0004

Else

PC = 0x00000004

3.软中断SWI

软中断异常发生时,处理器进入特权模式,执行一些特权模式下的操作系统功能。软中断异常发生时,处理器执行下列伪操作。

r14_svc = address of next instruction after the SWI instruction

SPSR_und = CPSR

CPSR[4∶0] = 0b10011 /*进入特权模式*/

CPSR[5] = 0 /*处理器进入ARM状态*/

/*CPSR[6]保持不变*/

CPSR[7] = 1 /*禁止外设中断*/

If high vectors configured then

PC = 0xffff0008

Else

PC = 0x00000008

4.预取指令异常

预取指令异常使由系统存储器报告的。当处理器试图去取一条被标记为预取无效的指令时,发生预取异常。

如果系统中不包含MMU时,指令预取异常中断处理程序只是简单地报告错误并退出。若包含MMU,引起异常的指令的物理地址被存储到内存中。

预取异常发生时,处理器执行下列伪操作。

r14_svc = address of the aborted instruction + 4

SPSR_und = CPSR

CPSR[4∶0] = 0b10111 /*进入特权模式*/

CPSR[5] = 0 /*处理器进入ARM状态*/

/*CPSR[6]保持不变*/

CPSR[7] = 1 /*禁止外设中断*/

If high vectors configured then

PC = 0xffff000C

Else

PC = 0x0000000C

异常或中断是用户程序中最基本的一种执行流程和形态。这部分主要对ARM架构下的异常中断做详细说明。

ARM有7种类型的异常,按优先级从高到低的排列如下:复位异常(Reset)、数据异常(Data Abort)、快速中断异常(FIQ)、外部中断异常(IRQ)、预取异常(Prefetch Abort)、软件中断(SWI)和未定义指令异常(Undefined instruction)。

3.4.1 异常种类

ARM体系结构中,存在7种异常处理。当异常发生时,处理器会把PC设置为一个特定的存储器地址。这一地址放在被称为向量表(vector table)的特定地址范围内。向量表的入口是一些跳转指令,跳转到专门处理某个异常或中断的子程序。

存储器映射地址0x00000000是为向量表(一组32位字)保留的。在有些处理器中,向量表可以选择定位在存储空间的高地址(从偏移量0xffff0000开始)。一些嵌入式操作系统,如Linux和Windows CE就要利用这一特性。

表3.4列出了ARM的7种异常。

表3.4 ARM的7种异常

异 常 类 型处理器模式执行低地址执行高地址

复位异常(Reset)特权模式0x000000000xFFFF0000

未定义指令异常(Undefined interrupt)未定义指令中止模式0x000000040xFFFF0004

软中断异常(Software Abort)特权模式0x000000080xFFFF0008

预取异常(Prefetch Abort)数据访问中止模式0x0000000C0xFFFF000C

数据异常(Data Abort)数据访问中止模式0x000000100xFFFF0010

外部中断请求IRQ外部中断请求模式0x000000180xFFFF0018

快速中断请求FIQ快速中断请求模式0x0000001C0xFFFF001C

异常处理向量表如图3.5所示。

当异常发生时,分组寄存器r14和SPSR用于保存处理器状态,操作伪指令如下。

R14_《exception_mode》 = return link

SPSR_《exception_mode》 = CPSR

CPSR[4∶0] = exception mode number

CPSR[5] = 0 /*进入ARM状态*/

If 《exception_mode》 = = reset or FIQ then

CPSR[6] = 1 /*屏蔽快速中断FIQ*/

CPSR[7] = 1 /*屏蔽外部中断IRQ*/

PC = exception vector address

图3.5 异常处理向量表

异常返回时,SPSR内容恢复到CPSR,连接寄存器r14的内容恢复到程序计数器PC。

1.复位异常

当处理器的复位引脚有效时,系统产生复位异常中断,程序跳转到复位异常中断处理程序处执行。复位异常中断通常用在下面两种情况下。

· 系统上电。

· 系统复位。

当复位异常时,系统执行下列伪操作。

R14_svc = UNPREDICTABLE value

SPSR_svc = UNPREDICTABLE value

CPSR[4∶0] = 0b10011 /*进入特权模式*/

CPSR[5] = 0 /*处理器进入ARM状态*/

CPSR[6] = 1 /*禁止快速中断*/

CPSR[7] = 1 /*禁止外设中断*/

If high vectors configured then

PC = 0xffff0000

Else

PC = 0x00000000

复位异常中断处理程序将进行一些初始化工作,内容与具体系统相关。下面是复位异常中断处理程序的主要功能。

· 设置异常中断向量表。

· 初始化数据栈和寄存器。

· 初始化存储系统,如系统中的MMU等。

· 初始化关键的I/O设备。

· 使能中断。

· 处理器切换到合适的模式。

· 初始化C变量,跳转到应用程序执行。

2.未定义指令异常

当ARM处理器执行协处理器指令时,它必须等待一个外部协处理器应答后,才能真正执行这条指令。若协处理器没有相应,则发生未定义指令异常。

未定义指令异常可用于在没有物理协处理器的系统上,对协处理器进行软件仿真,或通过软件仿真实现指令集扩展。例如,在一个不包含浮点运算的系统中,CPU遇到浮点运算指令时,将发生未定义指令异常中断,在该未定义指令异常中断的处理程序中可以通过其他指令序列仿真浮点运算指令。

仿真功能可以通过下面步骤实现。

① 将仿真程序入口地址链接到向量表中未定义指令异常中断入口处(0x00000004或0xffff0004),并保存原来的中断处理程序。

② 读取该未定义指令的bits[27∶24],判断其是否是一条协处理器指令。如果bits[27∶24]值为0b1110或0b110x,该指令是一条协处理器指令;否则,由软件仿真实现协处理器功能,可以同过bits[11∶8]来判断要仿真的协处理器功能(类似于SWI异常实现机制)。

③ 如果不仿真该未定义指令,程序跳转到原来的未定义指令异常中断的中断处理程序执行。

当未定义异常发生时,系统执行下列的伪操作。

r14_und = address of next instruction after the undefined instruction

SPSR_und = CPSR

CPSR[4∶0] = 0b11011 /*进入未定义指令模式*/

CPSR[5] = 0 /*处理器进入ARM状态*/

/*CPSR[6]保持不变*/

CPSR[7] = 1 /*禁止外设中断*/

If high vectors configured then

PC = 0xffff0004

Else

PC = 0x00000004

3.软中断SWI

软中断异常发生时,处理器进入特权模式,执行一些特权模式下的操作系统功能。软中断异常发生时,处理器执行下列伪操作。

r14_svc = address of next instruction after the SWI instruction

SPSR_und = CPSR

CPSR[4∶0] = 0b10011 /*进入特权模式*/

CPSR[5] = 0 /*处理器进入ARM状态*/

/*CPSR[6]保持不变*/

CPSR[7] = 1 /*禁止外设中断*/

If high vectors configured then

PC = 0xffff0008

Else

PC = 0x00000008

4.预取指令异常

预取指令异常使由系统存储器报告的。当处理器试图去取一条被标记为预取无效的指令时,发生预取异常。

如果系统中不包含MMU时,指令预取异常中断处理程序只是简单地报告错误并退出。若包含MMU,引起异常的指令的物理地址被存储到内存中。

预取异常发生时,处理器执行下列伪操作。

r14_svc = address of the aborted instruction + 4

SPSR_und = CPSR

CPSR[4∶0] = 0b10111 /*进入特权模式*/

CPSR[5] = 0 /*处理器进入ARM状态*/

/*CPSR[6]保持不变*/

CPSR[7] = 1 /*禁止外设中断*/

If high vectors configured then

PC = 0xffff000C

Else

PC = 0x0000000C

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章