资料下载

×

磁铁电源控制器的设计方案分析

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-10-21

摘要:介绍了一种基于DSP和FPGA的磁铁电源控制器的设计方案,阐述了该控制器硬件系统的组成,包括信号调理电路、中间数据处理部分、后端的驱动电路。同时给出了DSP和FPGA之间通过SPI接口通信的具体流程和输出PWM波形死区部分的控制流程。设计的磁铁电源控制器有很好的控制和运算能力,同时具有很好的灵活性和可靠性。

磁铁电源大多作为电源中的一种特种电源被广泛应用于加速器、质谱仪等设备,为磁铁提供特定的励磁电流以产生所需的磁场,对磁铁电源的基本要求来源于磁场特性,因此基于数字化电源控制器的磁铁电源为输出高精度的稳定励磁电流,以获得符合运行模式的稳定磁场结构提供了重要保证。文中介绍的磁铁电源控制器采用DSP和FPGA的双CPU结构,采用FPGA控制高精度模数转换器AD7679进行采样,通过DSP的SPI接口把采集到的数据送给DSP;由DSP运算处理后输出用来控制磁铁电源的带有死区的PWM波形。

1 控制器总体结构

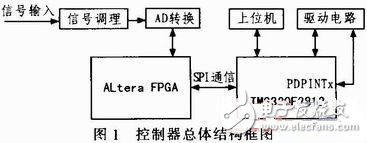

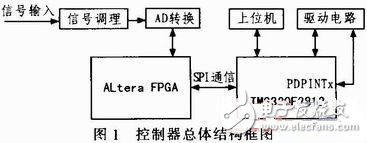

控制器采用DSP TMS320F2812为数字处理输出模块,以Altera公司的CvcloneⅢ系列FPGA控制前端AD进行数据采集,数据传输部分由FPGA与DSP的SPI接口完成。通过DSP的SCI串口与上位机实现通讯,显示并控制电源的运行状态,后端的驱动电路中实现主电路和驱动电路的隔离。控制器总体结构框图如图1所示。

2 硬件电路设计

2.1 信号调理电路

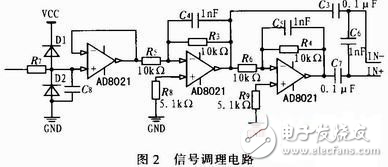

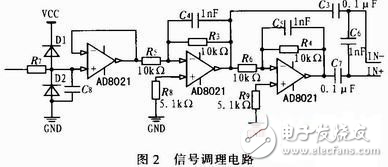

信号调理电路的主要作用是实现信号的放大和低通滤波。因为要保证将AD转换器的采集信号限制在0~+5 V之间,为防止大电流信号时产生过高的输入电压会损坏A/D端口,设计了电平限制保护电路。AD转换器输入采用差分输入方式,将单端信号转换为差分信号,实现比例放大,有效的滤除了高频噪声,便于AD对输入信号的高精度采集。图2为信号限幅、隔离、滤波和放大电路。

2.2 FPGA对AD的控制

本设计采用的AD7679是18位电荷分配的完全差分逐次逼近型模数转换器,具有570 ksps的采样速率,同时可以与5 V或3 V的数字逻辑电平兼容。为防止采样点在开关脉冲之上,系统出现振荡,可以使DSP在发出开关脉冲的同时给FPGA一个同步信号,作适当延时,等信号的尖峰脉冲消失后,FPGA再给ADC发出采样命令。AD操作分为空闲、开始AD转换、等待AD转换、读AD转换结果4个状态。在CONVST信号的下降沿后,开启转换过程,BUSY会自动置1,保持转换。当BUSY信号变为低电平,CONVST保持高电平时,AD7679处于数据采集阶段。FPGA对AD的控制如图3所示,实际的电路中,FPGA和AD转换器之间加入四通道的磁隔离器件ADuM1412进行数据隔离。

磁铁电源大多作为电源中的一种特种电源被广泛应用于加速器、质谱仪等设备,为磁铁提供特定的励磁电流以产生所需的磁场,对磁铁电源的基本要求来源于磁场特性,因此基于数字化电源控制器的磁铁电源为输出高精度的稳定励磁电流,以获得符合运行模式的稳定磁场结构提供了重要保证。文中介绍的磁铁电源控制器采用DSP和FPGA的双CPU结构,采用FPGA控制高精度模数转换器AD7679进行采样,通过DSP的SPI接口把采集到的数据送给DSP;由DSP运算处理后输出用来控制磁铁电源的带有死区的PWM波形。

1 控制器总体结构

控制器采用DSP TMS320F2812为数字处理输出模块,以Altera公司的CvcloneⅢ系列FPGA控制前端AD进行数据采集,数据传输部分由FPGA与DSP的SPI接口完成。通过DSP的SCI串口与上位机实现通讯,显示并控制电源的运行状态,后端的驱动电路中实现主电路和驱动电路的隔离。控制器总体结构框图如图1所示。

2 硬件电路设计

2.1 信号调理电路

信号调理电路的主要作用是实现信号的放大和低通滤波。因为要保证将AD转换器的采集信号限制在0~+5 V之间,为防止大电流信号时产生过高的输入电压会损坏A/D端口,设计了电平限制保护电路。AD转换器输入采用差分输入方式,将单端信号转换为差分信号,实现比例放大,有效的滤除了高频噪声,便于AD对输入信号的高精度采集。图2为信号限幅、隔离、滤波和放大电路。

2.2 FPGA对AD的控制

本设计采用的AD7679是18位电荷分配的完全差分逐次逼近型模数转换器,具有570 ksps的采样速率,同时可以与5 V或3 V的数字逻辑电平兼容。为防止采样点在开关脉冲之上,系统出现振荡,可以使DSP在发出开关脉冲的同时给FPGA一个同步信号,作适当延时,等信号的尖峰脉冲消失后,FPGA再给ADC发出采样命令。AD操作分为空闲、开始AD转换、等待AD转换、读AD转换结果4个状态。在CONVST信号的下降沿后,开启转换过程,BUSY会自动置1,保持转换。当BUSY信号变为低电平,CONVST保持高电平时,AD7679处于数据采集阶段。FPGA对AD的控制如图3所示,实际的电路中,FPGA和AD转换器之间加入四通道的磁隔离器件ADuM1412进行数据隔离。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章