资料下载

×

PCI高速测控系统结构研究设计方案

消耗积分:1 |

格式:rar |

大小:0.6 MB |

2017-10-23

随着数字信号处理芯片性价比的不断提高,数字信号处理的应用领域飞速发展,同时Pentium高速CPU的出现,要求有极高的数据通量予以支持,而低速的ISA总线在解决这些问题方面逐渐无能为力,取而代之的是高速的PCI总线。PCI总线可将高速外围设备直接挂在CPU总线上,33MHz/32位时数据传输速率可达132MB/s,66MHz/64位时更是性能加倍,打破了数据传输速率的瓶颈,使得CPU的性能得到充分发挥。如果采用美国TI公司生产的高速高性能数字信号处理器DSP取代原来的单片机作为板载CPU,可以充分利用PCI总线的优点直接将采集的数据传到微机内存,有效地解决了数据的实时传输和存储问题。

测控系统的硬件组成

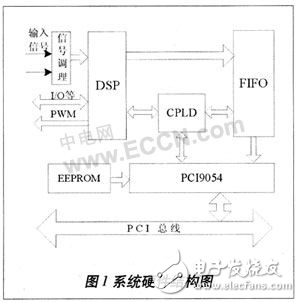

系统基本硬件结构如图1所示。整个高速测控系统主要由信号调理电路、DSP模块、FIFC)存储器、CPLD控制电路、PC19054接口芯片等组成。系统采用主从结构,PC机作为上位机,用于完成对系统的控制(如AD转换的开始、DSP复位、中断响应、数据接收与处理等)。DSP作为下位机,用于完成数据的采集与处理、PWM波以及其他外围信号的控制等。

DSP测控模块介绍

系统采用的DSP芯片为TI公司的TMS320LF2407。电路设计时,利用的DSP内部的16通道A/D转换实现数据采集,DSP与FIFO的电路接口电压都为3.3V,可实现无缝连接,DSP的数据总线直接与FIFO的数据输入端口相连,DSP与FIFO的时钟频率应设为相同。这样,无需插入等待周期,控制信号经CPLD直接转换为FIFO的读写信号,实现数据的高速存储。

先进先出存储器

在DMA传输方式下,由于PCI9054内部的FIFO只有32级深度,实时传送高速数据时,PCI9054内部的FIFO会很快存满,而DSP内的数据仍会源源不断的传送过来,易造成数据的丢失,因此必须要扩展外部FIFO。

本系统采用I D T公司高速CMOS同步FIFO芯片IDT72V3660,它的容量为4096×36bit;有高达100MHz的读写速度;可以兼容3.3V和5V两种接口电压。该FIFO具有标准的“满”(FF#)、“半满”(HF#)、“空”(EF#)等标志。系统可以根据这些标志信号控制对FIFO的读写操作。在CPLD的逻辑控制下,当WEN#有效时,在WCLK的每一个上升沿,FIFO会把输人数据线上的数据存入内部存储器。当REN#有效且输出允许(OE#有效)时,在RCLK的每一个上升沿,FIFO会把内部存储器中的数据发送到输出数据总线上(低电平用“#”表示)。

控制逻辑芯片CPLD

本系统采用Altera公司的EPM7 128来实现系统的逻辑控制,主要包括DSP控制逻辑、FIFO控制逻辑、PCI9054接口控制逻辑三个部分,其中,对PC219054的逻辑控制是设计的重点。设计中利用MaxPlusⅡ软件进行VHDL语言编程、仿真和调试。

PCI9054及外部接口分析

PCI与板载CPU的桥接有两种设计方案,一种是采用FPGA,通过软件编程实现硬件功能。另一种是利用专用PCI桥接芯片,适合快速开发的场合。

本系统采用PLX公司的PCI总线专用接口控制芯片PC19054。它符合PCIV2.1和PCIV2_2规范;可同时支持3.3V和5V两种信号环境;提供了两个独立的可编程DMA控制器;内部有6种可编程FIFO,以实现零等待突发传输及局部总线和PCI总线之间的异步操作;在PCI总线端支持33MHz/32位,传输速率最高可达132MB/s;在局部端可编程实现8/16/32位的数据宽度,支持复用/非复用的32位地址/数据,时钟最高可达50MHz。

PCI9054局部总线可工作在M、J、C三种模式,M模式是专门为Motorola公司的 MPC850和MPC860提供直接非复用的接口;J模式地址/数据线复用;C模式与J模式差别不大,但地址/数据线非复用,更符合连接习惯。本设计采用C模式。

PCI9054的数据传输模式可分为主模式、从模式、DMA模式。模式的选择主要根据硬件设计者对硬件的设计需要而定。本系统采用DMA模式,在DMA传输模式下,PCI9054既是PCI端的主控方,又是局部端的主控方。

PCI9054集成了两个互相独立的DMA通道,每个通道都支持Block DMA和Scatter/(3ather DMA,其中通道0还支持请求(Demand)DMA传输方式。当有通道进行DMA传输时,DMA控制器将发起对局部总线和PCI总线操作,其传输过程如图2所示。

PC219054提供了三个物理总线接口:PCI总线接口、EEPROM接口、局部总线接口。PCI总线接口依照PCI扩展板上定义的引脚分配情况将彼此对应的信号连接在一起即可。本系统采用的EEPROM为4K、3.3V串行的93LC66B,通过对PCI时钟分频来产生EEPROM时钟,内部存放PCI9054的配置信息,系统加电时PCI9054自动加载EEPROM中的配置信息,并由BIOS通过PCI总线对配置寄存器读写,来完成各种控制功能。接口电路如图3所示。

测控系统的硬件组成

系统基本硬件结构如图1所示。整个高速测控系统主要由信号调理电路、DSP模块、FIFC)存储器、CPLD控制电路、PC19054接口芯片等组成。系统采用主从结构,PC机作为上位机,用于完成对系统的控制(如AD转换的开始、DSP复位、中断响应、数据接收与处理等)。DSP作为下位机,用于完成数据的采集与处理、PWM波以及其他外围信号的控制等。

DSP测控模块介绍

系统采用的DSP芯片为TI公司的TMS320LF2407。电路设计时,利用的DSP内部的16通道A/D转换实现数据采集,DSP与FIFO的电路接口电压都为3.3V,可实现无缝连接,DSP的数据总线直接与FIFO的数据输入端口相连,DSP与FIFO的时钟频率应设为相同。这样,无需插入等待周期,控制信号经CPLD直接转换为FIFO的读写信号,实现数据的高速存储。

先进先出存储器

在DMA传输方式下,由于PCI9054内部的FIFO只有32级深度,实时传送高速数据时,PCI9054内部的FIFO会很快存满,而DSP内的数据仍会源源不断的传送过来,易造成数据的丢失,因此必须要扩展外部FIFO。

本系统采用I D T公司高速CMOS同步FIFO芯片IDT72V3660,它的容量为4096×36bit;有高达100MHz的读写速度;可以兼容3.3V和5V两种接口电压。该FIFO具有标准的“满”(FF#)、“半满”(HF#)、“空”(EF#)等标志。系统可以根据这些标志信号控制对FIFO的读写操作。在CPLD的逻辑控制下,当WEN#有效时,在WCLK的每一个上升沿,FIFO会把输人数据线上的数据存入内部存储器。当REN#有效且输出允许(OE#有效)时,在RCLK的每一个上升沿,FIFO会把内部存储器中的数据发送到输出数据总线上(低电平用“#”表示)。

控制逻辑芯片CPLD

本系统采用Altera公司的EPM7 128来实现系统的逻辑控制,主要包括DSP控制逻辑、FIFO控制逻辑、PCI9054接口控制逻辑三个部分,其中,对PC219054的逻辑控制是设计的重点。设计中利用MaxPlusⅡ软件进行VHDL语言编程、仿真和调试。

PCI9054及外部接口分析

PCI与板载CPU的桥接有两种设计方案,一种是采用FPGA,通过软件编程实现硬件功能。另一种是利用专用PCI桥接芯片,适合快速开发的场合。

本系统采用PLX公司的PCI总线专用接口控制芯片PC19054。它符合PCIV2.1和PCIV2_2规范;可同时支持3.3V和5V两种信号环境;提供了两个独立的可编程DMA控制器;内部有6种可编程FIFO,以实现零等待突发传输及局部总线和PCI总线之间的异步操作;在PCI总线端支持33MHz/32位,传输速率最高可达132MB/s;在局部端可编程实现8/16/32位的数据宽度,支持复用/非复用的32位地址/数据,时钟最高可达50MHz。

PCI9054局部总线可工作在M、J、C三种模式,M模式是专门为Motorola公司的 MPC850和MPC860提供直接非复用的接口;J模式地址/数据线复用;C模式与J模式差别不大,但地址/数据线非复用,更符合连接习惯。本设计采用C模式。

PCI9054的数据传输模式可分为主模式、从模式、DMA模式。模式的选择主要根据硬件设计者对硬件的设计需要而定。本系统采用DMA模式,在DMA传输模式下,PCI9054既是PCI端的主控方,又是局部端的主控方。

PCI9054集成了两个互相独立的DMA通道,每个通道都支持Block DMA和Scatter/(3ather DMA,其中通道0还支持请求(Demand)DMA传输方式。当有通道进行DMA传输时,DMA控制器将发起对局部总线和PCI总线操作,其传输过程如图2所示。

PC219054提供了三个物理总线接口:PCI总线接口、EEPROM接口、局部总线接口。PCI总线接口依照PCI扩展板上定义的引脚分配情况将彼此对应的信号连接在一起即可。本系统采用的EEPROM为4K、3.3V串行的93LC66B,通过对PCI时钟分频来产生EEPROM时钟,内部存放PCI9054的配置信息,系统加电时PCI9054自动加载EEPROM中的配置信息,并由BIOS通过PCI总线对配置寄存器读写,来完成各种控制功能。接口电路如图3所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章