资料下载

×

现代DSP芯片功能的扩展概述

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-10-25

数字信号处理器(DSP)做某些模拟工作比模拟电路要出色,因此得以生存。在某些情况下,由于成本或复杂性的原因,任务甚至不能考虑用模拟电路,DSP仍然是一种可行的选择,在很多情况下可以轻松地完成那些任务。

这是因为DSP进行算术运算既好又快,如加法和乘法。聪明的数学家和工程师利用了这一实际,通过创造算法来解决主要采用两种数学运算的复杂的信号处理任务。

如今的DSP芯片不仅仅只是一个优秀的处理引擎。芯片上还集成了存储子系统、高速接口、I/O等等。增加这些部件的目的是为了提高整体性能,降低功耗以及针对特殊的处理任务。

为了更好地理解各种DSP芯片的可用选项以及器件各部分是如何配合作为一个整体,分析当今市场上几种有代表性的DSP是有帮助的。我们将仔细研究单核、单核加微控制器以及多核DSP芯片的例子。

单核DSP芯片

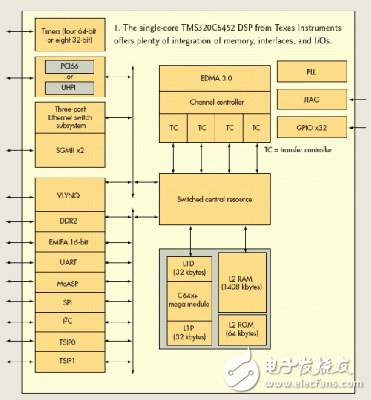

认为DSP芯片有一个单DSP核是很自然的,例如,TI的TMS320C6452(图1)。此芯片是高性能固点DSP的TMS320C64x+家族的一员,针对工艺密集的多通道电信基础设施和医用成像系统。DSP核只不过是芯片设计的一部分,芯片的其余部分还包括存储器、I/O以及其他功能模块。

C6452 DSP集成了组织为两级存储子系统的片上存储器。一级(L1)程序和数据存储器每个都是32k字节。此存储器可配置为映射RAM、高速缓存,或者两者的某种组合。

当配置为高速缓存时,L1程序(L1P)是一个直接映射高速缓存,而L1数据(L1D)是一个双向指令集结合高速缓存。二级(L2)存储在程序与数据空间之间共享。L2存储也能配置为映射RAM、高速缓存或者两者的某种组合。设计师可使用片上存储器为其项目增加特色。

C6452还包括两个串行吉比特媒体独立接口(SGMII)以太媒体接入控制(MAC)口和一个吉比特开关。此开关通过自动监控数据流以确保只有一个合适的TI将决策门加到所能的开关上,例如,用来辨别语音和数据通信,以提高多芯片设计的效率。如果DSP全部用于语音处理,就会阻止数据流进入,这样可更有效地使用其处理带宽。此外,器件具有两个电信串行接口端(TSIP),可无缝连接至常见电信串行数据流。

C6452上的其他I/O有一个66MHz PCI接口或通用主机端接口(UHPI);一个到外部存储器的双数据率(DDR2)接口;TI开发的专利串行通信接口VLYNQ;一个16位外部存储器接口(EMIFA);一个多通道通用音频串行口(McASP);以及其他熟悉的接口。从此DSP的I/O判断,可以肯定它是用于电信应用。其他应用用的是不同的I/O。

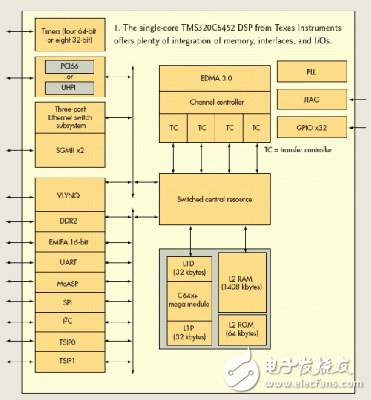

C6452和TI其他几款DSP的核心是C64x mega模块,其组成包括几个元件:C64x+处理器、L1程序和数据存储控制器、L2存储控制器、内部DMA(IDMA)、中断控制器、掉电控制器以及外部存储控制器(图2)。Mega模块还支持对L1P、L1D和L2存储器的存储保护。此外还提供mega模块资源的带宽管理。

这是因为DSP进行算术运算既好又快,如加法和乘法。聪明的数学家和工程师利用了这一实际,通过创造算法来解决主要采用两种数学运算的复杂的信号处理任务。

如今的DSP芯片不仅仅只是一个优秀的处理引擎。芯片上还集成了存储子系统、高速接口、I/O等等。增加这些部件的目的是为了提高整体性能,降低功耗以及针对特殊的处理任务。

为了更好地理解各种DSP芯片的可用选项以及器件各部分是如何配合作为一个整体,分析当今市场上几种有代表性的DSP是有帮助的。我们将仔细研究单核、单核加微控制器以及多核DSP芯片的例子。

单核DSP芯片

认为DSP芯片有一个单DSP核是很自然的,例如,TI的TMS320C6452(图1)。此芯片是高性能固点DSP的TMS320C64x+家族的一员,针对工艺密集的多通道电信基础设施和医用成像系统。DSP核只不过是芯片设计的一部分,芯片的其余部分还包括存储器、I/O以及其他功能模块。

C6452 DSP集成了组织为两级存储子系统的片上存储器。一级(L1)程序和数据存储器每个都是32k字节。此存储器可配置为映射RAM、高速缓存,或者两者的某种组合。

当配置为高速缓存时,L1程序(L1P)是一个直接映射高速缓存,而L1数据(L1D)是一个双向指令集结合高速缓存。二级(L2)存储在程序与数据空间之间共享。L2存储也能配置为映射RAM、高速缓存或者两者的某种组合。设计师可使用片上存储器为其项目增加特色。

C6452还包括两个串行吉比特媒体独立接口(SGMII)以太媒体接入控制(MAC)口和一个吉比特开关。此开关通过自动监控数据流以确保只有一个合适的TI将决策门加到所能的开关上,例如,用来辨别语音和数据通信,以提高多芯片设计的效率。如果DSP全部用于语音处理,就会阻止数据流进入,这样可更有效地使用其处理带宽。此外,器件具有两个电信串行接口端(TSIP),可无缝连接至常见电信串行数据流。

C6452上的其他I/O有一个66MHz PCI接口或通用主机端接口(UHPI);一个到外部存储器的双数据率(DDR2)接口;TI开发的专利串行通信接口VLYNQ;一个16位外部存储器接口(EMIFA);一个多通道通用音频串行口(McASP);以及其他熟悉的接口。从此DSP的I/O判断,可以肯定它是用于电信应用。其他应用用的是不同的I/O。

C6452和TI其他几款DSP的核心是C64x mega模块,其组成包括几个元件:C64x+处理器、L1程序和数据存储控制器、L2存储控制器、内部DMA(IDMA)、中断控制器、掉电控制器以及外部存储控制器(图2)。Mega模块还支持对L1P、L1D和L2存储器的存储保护。此外还提供mega模块资源的带宽管理。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章