资料下载

×

一种高速并行位同步结构设计研究

消耗积分:1 |

格式:rar |

大小:0.66 MB |

2017-10-30

随着卫星技术和星上有效载荷技术的发展,卫星数传系统对信息传输速率的要求也越来越高,从过去的kbps 提高到目前几百Mbps,末来高速数传系统传输速率将达G 量级。随着传输速率的提升,如何实时处理高速数据成为关键。

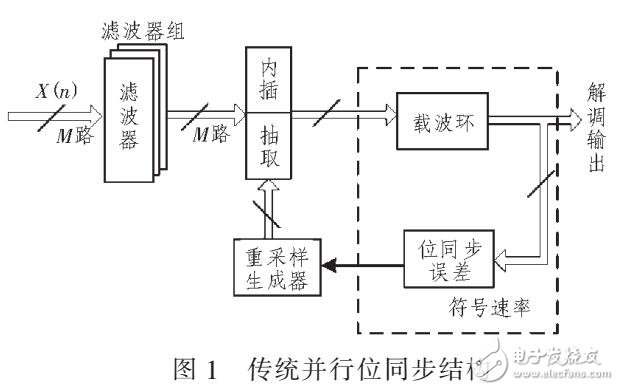

美国JPL 实验室在97 年提出了APRX 结构,采用并行结构实现高速全数字解调,国内也有许多针对高速数据解调方面的研究|。并行结构的解调器中的匹配滤波器个数与并行路数成比,资源消耗巨大,且位同步数据抽取需要大量选择开关,成为FPGA 实现的一个难点。研究了并行结构的频域匹配滤波器设计,给出了一种频域并行解调结构。文中将匹配滤波与位同步相结合,通过实时更新滤波器系数,同时实现滤波、内插、抽取功能,滤波器组输出速率降低为符号速率。降低了并行结构中匹配滤波器的数量,从而达到减少资源消耗的目的。给出了滤波器系数的计算过程及具体方法,分析了该结构的资源消耗情况。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章