资料下载

×

高性能数字信号处理器TMS320LF2407A及应用分析

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-11-01

1 引言

数字信号处理器(DSP)已经发展了20多年,最初仅在信号处理领域内应用。近年来, 随着半导体技术的发展,其高速运算能力使很多复杂的控制算法和功能得以实现,同时将实时处理能力和控制器的外设功能集于一身,在控制领域内也得到很好的应用。数字控制系统克服了模拟控制系统电路功能单一、控制精度不高的缺点,它抗干扰能力强,可靠性高,可实现复杂控制,增强了控制的灵活性。

TMS320LF2407A是美国TI公司推出的新型高性能16位定点数字信号处理器,它专门为数字控制设计,集DSP的高速信号处理能力及适用于控制的优化外围电路于一体,在数字控制系统中得以广泛应用 [1]。本文介绍其体系结构、功能特性及其在控制领域中的应用,为数字控制系统的设计提供参考。

2 体系结构和功能特性

2.1 系统组成

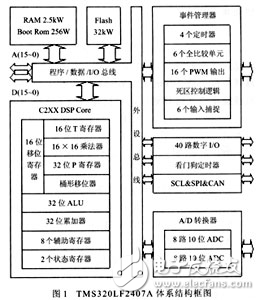

TMS320LF2407A系统组成包括:40MHz、40MIPS的低电压3.3V CPU、片内存储器、事件管理器模块、片内集成外围设备[2]。其体系结构框图如图1所示。

2.2 CPU及总线结构

TMS320LF2407A的CPU是基于TMS320C2XX的16位定点低功耗内核。体系结构采用四级流水线技术加快程序的执行,可在一个处理周期内完成乘法、加法和移位运算。其中央算术逻辑单元(CALU)是一个独立的算术单元,它包括一个32位算术逻辑单元(ALU)、一个32位累加器、一个16×16位乘法器(MUL)和一个16位桶形移位器,同时乘法器和累加器内部各包含一个输出移位器。完全独立于CALU的辅助寄存器单元(ARAU)包含八个16位辅助寄存器,其主要功能是在CALU操作的同时执行八个辅助寄存器(AR7至AR0)上的算术运算。两个状态寄存器ST0 和ST1用于实现CPU各种状态的保存。

TMS320LF2407A采用增强的哈佛结构,芯片内部具有六条16位总线,即程序地址总线(PAB)、数据读地址总线(DRAB)、数据写地址总线(DWAB)、程序读总线(PRDB)、数据读总线(DRDB)、数据写总线(DWEB),其程序存储器总线和数据存储器总线相互独立,支持并行的程序和操作数寻址,因此CPU的读/写可在同一周期内进行,这种高速运算能力使自适应控制、卡尔曼滤波、神经网络、遗传算法等复杂控制算法得以实现。

2.3 存储器配置

TMS320LF2407A地址映象被组织为三个可独立选择的空间:程序存储器(64K)、数据存储器(64K)、输入/输出(I/O)空间(64K)。这些空间提供了共192K字的地址范围。

其片内存储器资源包括:544字×16位的双端口数据/程序DARAM、2K字×16位的单端口数据/程序SARAM、片内32K×16位的Flash程序存储器、256字×16位片上Boot ROM、片上Flash/ROM具有可编程加密特性。

TMS320LF2407A的指令集有三种基本的存储器寻址方式:立即寻址方式、直接寻址方式、间接寻址方式。

数字信号处理器(DSP)已经发展了20多年,最初仅在信号处理领域内应用。近年来, 随着半导体技术的发展,其高速运算能力使很多复杂的控制算法和功能得以实现,同时将实时处理能力和控制器的外设功能集于一身,在控制领域内也得到很好的应用。数字控制系统克服了模拟控制系统电路功能单一、控制精度不高的缺点,它抗干扰能力强,可靠性高,可实现复杂控制,增强了控制的灵活性。

TMS320LF2407A是美国TI公司推出的新型高性能16位定点数字信号处理器,它专门为数字控制设计,集DSP的高速信号处理能力及适用于控制的优化外围电路于一体,在数字控制系统中得以广泛应用 [1]。本文介绍其体系结构、功能特性及其在控制领域中的应用,为数字控制系统的设计提供参考。

2 体系结构和功能特性

2.1 系统组成

TMS320LF2407A系统组成包括:40MHz、40MIPS的低电压3.3V CPU、片内存储器、事件管理器模块、片内集成外围设备[2]。其体系结构框图如图1所示。

2.2 CPU及总线结构

TMS320LF2407A的CPU是基于TMS320C2XX的16位定点低功耗内核。体系结构采用四级流水线技术加快程序的执行,可在一个处理周期内完成乘法、加法和移位运算。其中央算术逻辑单元(CALU)是一个独立的算术单元,它包括一个32位算术逻辑单元(ALU)、一个32位累加器、一个16×16位乘法器(MUL)和一个16位桶形移位器,同时乘法器和累加器内部各包含一个输出移位器。完全独立于CALU的辅助寄存器单元(ARAU)包含八个16位辅助寄存器,其主要功能是在CALU操作的同时执行八个辅助寄存器(AR7至AR0)上的算术运算。两个状态寄存器ST0 和ST1用于实现CPU各种状态的保存。

TMS320LF2407A采用增强的哈佛结构,芯片内部具有六条16位总线,即程序地址总线(PAB)、数据读地址总线(DRAB)、数据写地址总线(DWAB)、程序读总线(PRDB)、数据读总线(DRDB)、数据写总线(DWEB),其程序存储器总线和数据存储器总线相互独立,支持并行的程序和操作数寻址,因此CPU的读/写可在同一周期内进行,这种高速运算能力使自适应控制、卡尔曼滤波、神经网络、遗传算法等复杂控制算法得以实现。

2.3 存储器配置

TMS320LF2407A地址映象被组织为三个可独立选择的空间:程序存储器(64K)、数据存储器(64K)、输入/输出(I/O)空间(64K)。这些空间提供了共192K字的地址范围。

其片内存储器资源包括:544字×16位的双端口数据/程序DARAM、2K字×16位的单端口数据/程序SARAM、片内32K×16位的Flash程序存储器、256字×16位片上Boot ROM、片上Flash/ROM具有可编程加密特性。

TMS320LF2407A的指令集有三种基本的存储器寻址方式:立即寻址方式、直接寻址方式、间接寻址方式。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章