资料下载

×

便携数字存储示波表设计方案解析

消耗积分:1 |

格式:rar |

大小:0.1 MB |

2017-11-06

随着大规模集成电路技术、信号分析与处理技术及嵌入式微处理器软硬件技术的迅速发展,现代电子测量技术与仪器领域也在不断探讨新的仪器结构和新的测试理论及方法。集数字存储示波器、数字万用表、频率计三者功能于一体的便携式数字存储示波表正代表了当代电子测量仪器发展的一种新趋势。便携式数字存储示波表具有体积小、重量轻、成本低、不需交流供电、可靠性高、使用简便等一系列特性,非常适合于使用在有电源、空间、运输等条件限制的环境下。

便携式数字存储示波表集A/D技术、ASIC技术、DSP技术、LCD显示技术于一体,具有极高的技术含量、很强的实用性和巨大的市场潜力。目前国外已有较成熟的产品,而国内在该领域的研究尚属起步阶段。本文所述方案采用嵌入式设计技术,成功地实现了对被测信号的实时处理与分析。

2. 便携式数字存储示波表的硬件设计思想

2.1 硬件系统结构设计

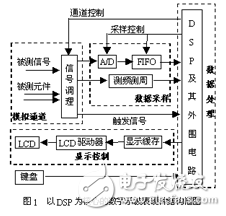

便携式数字存储示波表硬件上主要包括模拟通道、数据采样、数据处理、显示控制等模块。图1所示为一种传统的以微控制器(DSP)为核心的示波表结构设计方案。该方案的缺点是:系统只能将DSP做为核心控制器件,造成DSP任务繁重、接口复杂。

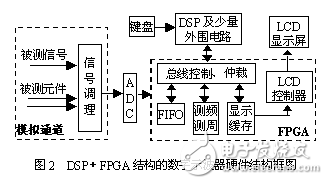

为解决上述问题,本文采用了基于DSP+FPGA结构的嵌入式设计方案,如图2所示。其中FPGA主要集成了以下部件:

(1) 2K字节的FIFO及FIFO控制器:FIFO用来缓存高速ADC采集的信号数据。系统无有效触发信号时FIFO工作在环形方式,

不断写入ADC送来的采样数据;当触发信号有效后,FIFO工作在桶形方式,FIFO控制器将根据DSP预先写入的预触发/后触发时间 控制字设置FIFO读指针位置,一旦FIFO写满后就停止写入,并由FIFO控制器通知DSP取走这一屏的采样数据;

(2) 2K字节的显示缓存:用以缓存从DSP送来的LCD显示数据,并等待LCD控制器取走送LCD显示;

(3) 外围控制器部分:

a. 测频测周电路:接收模拟通道送来的整形后的测量信号,测得被测信号的频率/周期值并等待DSP读取;

b. 采样频率控制电路:根据DSP写入的控制字分别控制ADC采样频率及FIFO写频率,以最大限度地利用有限的FIFO空间实现宽频采样;

c. 触发仲裁:确定是否抑制模拟通道送来的触发信号;

d. 总线仲裁:对DSP产生的地址信号及控制信号进行译码以完成对外部设备的操作,并负责协调FIFO和显示缓冲可能存在的读/写冲突;

e. LCD控制器:产生LCD显示所需的各种时序信号,并负责从显示缓存中读取数据送LCD显示屏;

可见,本设计将除模拟通道、ADC、DSP及LCD显示屏之外的绝大部分功能部件都集成在FPGA内部。FPGA硬件在解析DSP预先写入的少量控制字后即可自动完成数据采样、信号频率/周期测量以及波形显示等底层控制功能,而DSP则被解放出来主要负责数据编码、波形恢复及人机界面等上层数据的控制处理。

总之,为最大限度地充分发挥可编程ASIC芯片在嵌入系统设计中的作用,本设计使用FPGA分担部分系统控制任务,使DSP能够更好、更有效地发挥其数据处理的特长;同时,FPGA的使用使系统中分立功能部件大大减少,也有效地缩减了系统的体积和功耗,增加了系统的可靠性。

便携式数字存储示波表集A/D技术、ASIC技术、DSP技术、LCD显示技术于一体,具有极高的技术含量、很强的实用性和巨大的市场潜力。目前国外已有较成熟的产品,而国内在该领域的研究尚属起步阶段。本文所述方案采用嵌入式设计技术,成功地实现了对被测信号的实时处理与分析。

2. 便携式数字存储示波表的硬件设计思想

2.1 硬件系统结构设计

便携式数字存储示波表硬件上主要包括模拟通道、数据采样、数据处理、显示控制等模块。图1所示为一种传统的以微控制器(DSP)为核心的示波表结构设计方案。该方案的缺点是:系统只能将DSP做为核心控制器件,造成DSP任务繁重、接口复杂。

为解决上述问题,本文采用了基于DSP+FPGA结构的嵌入式设计方案,如图2所示。其中FPGA主要集成了以下部件:

(1) 2K字节的FIFO及FIFO控制器:FIFO用来缓存高速ADC采集的信号数据。系统无有效触发信号时FIFO工作在环形方式,

不断写入ADC送来的采样数据;当触发信号有效后,FIFO工作在桶形方式,FIFO控制器将根据DSP预先写入的预触发/后触发时间 控制字设置FIFO读指针位置,一旦FIFO写满后就停止写入,并由FIFO控制器通知DSP取走这一屏的采样数据;

(2) 2K字节的显示缓存:用以缓存从DSP送来的LCD显示数据,并等待LCD控制器取走送LCD显示;

(3) 外围控制器部分:

a. 测频测周电路:接收模拟通道送来的整形后的测量信号,测得被测信号的频率/周期值并等待DSP读取;

b. 采样频率控制电路:根据DSP写入的控制字分别控制ADC采样频率及FIFO写频率,以最大限度地利用有限的FIFO空间实现宽频采样;

c. 触发仲裁:确定是否抑制模拟通道送来的触发信号;

d. 总线仲裁:对DSP产生的地址信号及控制信号进行译码以完成对外部设备的操作,并负责协调FIFO和显示缓冲可能存在的读/写冲突;

e. LCD控制器:产生LCD显示所需的各种时序信号,并负责从显示缓存中读取数据送LCD显示屏;

可见,本设计将除模拟通道、ADC、DSP及LCD显示屏之外的绝大部分功能部件都集成在FPGA内部。FPGA硬件在解析DSP预先写入的少量控制字后即可自动完成数据采样、信号频率/周期测量以及波形显示等底层控制功能,而DSP则被解放出来主要负责数据编码、波形恢复及人机界面等上层数据的控制处理。

总之,为最大限度地充分发挥可编程ASIC芯片在嵌入系统设计中的作用,本设计使用FPGA分担部分系统控制任务,使DSP能够更好、更有效地发挥其数据处理的特长;同时,FPGA的使用使系统中分立功能部件大大减少,也有效地缩减了系统的体积和功耗,增加了系统的可靠性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章