资料下载

×

微带线和带状线设计

消耗积分:1 |

格式:rar |

大小:0.6 MB |

2017-11-08

人们撰写了大量文章来阐述如何端接PCB走线特性阻抗以避免信号反射。但是,妥善运用传输线路技术的时机尚未说清楚。

下面总结了针对逻辑信号的一条成熟的适用性指导方针。

当PCB走线单向传播延时等于或大于施加信号上升/下降时间(以最快边沿为准)时端接传输线路特性阻抗。例如,在Er = 4.0介电质上2英寸微带线的延时约270 ps。严格贯彻上述规则,只要信号上升时间不到~500 ps,端接是适当的。

更保守的规则是使用2英寸(PCB走线长度)/纳秒(上升/下降时间)规则。如果信号走线超过此走线长度/速度准则,则应使用端接。例如,如果高速逻辑上升/下降时间为5 ns,PCB走线等于或大于10英寸(其中测量长度包括曲折线),就应端接其特性阻抗。

在模拟域内,必须注意,运算放大器和其他电路也应同样适用这条2英寸/纳秒指导方针,以确定是否需要传输线路技术。例如,如果放大器必须输出最大频率fmax,则等效上升时间tr和这个fmax相关。这个限制上升时间tr可计算如下:

tr=0.35/fmax 等式1

然后将tr乘以2英寸/纳秒来计算最大PCB走线长度。例如,最大频率100 MHz对应于3.5 ns的上升时间,所以载送此信号的7英寸或以上走线应视为传输线路。

PCB板上受控阻抗走线的设计

在受控阻抗设计中,可以采用多种走线几何形状,既可与PCB布局图合二为一,也可与其相结合。在下面的讨论中,基本模式遵循IPC标准2141A的规定。请注意,下面的图示中将使用术语“接地层”。需要了解的是,该接地层实际上是一个大面积、低阻抗的参考层。在实践中,可能是一个接地层或电源层,假定二者的交流电位均为零。

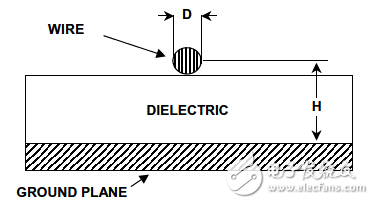

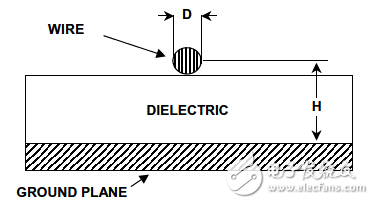

首先是简单的平面上布线形式的传输线路,也称微带线。图1所示为横截面视图。这类传输线路可能是实验板中使用的信号线。其构成非常简单,一条分立的绝缘线以固定间距分布于接地层上。介电质既可能是线材的绝缘层,也可能是该绝缘层与空气的结合体。

图1:一种阻抗既定的微带线传输线路由一条分布于接地层的绝缘线形成

该线路的阻抗(单位:欧姆)可以用等式2估算。其中,D为导体直径,H为线材在接地层上的间距, εr为介电常数。

等式2

等式2

对于与PCB相融合的图形,有多种几何模型可供选择,分为单端和差分两类。这些在IPC标准2141A(见参考文献1)中有详细说明,这里对两个常见示例略加说明。

在开始进行任何基于PCB传输线路设计时,必须知道,有大量的等式都声称适用于此类设计。此时,一个极其重要的问题就是,“哪些等式是精确的呢?”不幸的 是,没有一个等式是完全精确的!所有现有等式都是近似值,因而,其精度不尽相同,取决于具体情况。最知名也是引用最多的是参考文献1中给出的等式,但是, 即使这些等式也存在一些应用问题。

下面总结了针对逻辑信号的一条成熟的适用性指导方针。

当PCB走线单向传播延时等于或大于施加信号上升/下降时间(以最快边沿为准)时端接传输线路特性阻抗。例如,在Er = 4.0介电质上2英寸微带线的延时约270 ps。严格贯彻上述规则,只要信号上升时间不到~500 ps,端接是适当的。

更保守的规则是使用2英寸(PCB走线长度)/纳秒(上升/下降时间)规则。如果信号走线超过此走线长度/速度准则,则应使用端接。例如,如果高速逻辑上升/下降时间为5 ns,PCB走线等于或大于10英寸(其中测量长度包括曲折线),就应端接其特性阻抗。

在模拟域内,必须注意,运算放大器和其他电路也应同样适用这条2英寸/纳秒指导方针,以确定是否需要传输线路技术。例如,如果放大器必须输出最大频率fmax,则等效上升时间tr和这个fmax相关。这个限制上升时间tr可计算如下:

tr=0.35/fmax 等式1

然后将tr乘以2英寸/纳秒来计算最大PCB走线长度。例如,最大频率100 MHz对应于3.5 ns的上升时间,所以载送此信号的7英寸或以上走线应视为传输线路。

PCB板上受控阻抗走线的设计

在受控阻抗设计中,可以采用多种走线几何形状,既可与PCB布局图合二为一,也可与其相结合。在下面的讨论中,基本模式遵循IPC标准2141A的规定。请注意,下面的图示中将使用术语“接地层”。需要了解的是,该接地层实际上是一个大面积、低阻抗的参考层。在实践中,可能是一个接地层或电源层,假定二者的交流电位均为零。

首先是简单的平面上布线形式的传输线路,也称微带线。图1所示为横截面视图。这类传输线路可能是实验板中使用的信号线。其构成非常简单,一条分立的绝缘线以固定间距分布于接地层上。介电质既可能是线材的绝缘层,也可能是该绝缘层与空气的结合体。

图1:一种阻抗既定的微带线传输线路由一条分布于接地层的绝缘线形成

该线路的阻抗(单位:欧姆)可以用等式2估算。其中,D为导体直径,H为线材在接地层上的间距, εr为介电常数。

等式2

等式2对于与PCB相融合的图形,有多种几何模型可供选择,分为单端和差分两类。这些在IPC标准2141A(见参考文献1)中有详细说明,这里对两个常见示例略加说明。

在开始进行任何基于PCB传输线路设计时,必须知道,有大量的等式都声称适用于此类设计。此时,一个极其重要的问题就是,“哪些等式是精确的呢?”不幸的 是,没有一个等式是完全精确的!所有现有等式都是近似值,因而,其精度不尽相同,取决于具体情况。最知名也是引用最多的是参考文献1中给出的等式,但是, 即使这些等式也存在一些应用问题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章