资料下载

×

分析ADC中的集成式容性PGA之重新定义性能

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-11-10

ADI专利的容性可编程增益放大器(PGA)相比传统的阻性PGA具有更佳的性能,包括针对模拟输入信号的更高共模电压抑制能力。

本文描述了斩波容性放大器的工作原理,强调了需要放大传感器小信号至接近供电轨——比如温度测量(RTD或热电偶)和惠斯登电桥——时,此架构的优势。

Σ-Δ型模数转换器(ADC)广泛用于传感器具有较小输出电压范围和带宽的应用中(比如应变计或热敏电阻),因为这种架构提供高动态范围。具有高动态范围是因为,相比其它ADC架构,它具有低噪声性能。

Σ-Δ型转换器基于两条原理工作:过采样和噪声整形。当ADC对输入信号进行采样时,独立于采样频率的量化噪声会在直到采样频率一半的整个频谱内扩散。因此,如果输入信号以比奈奎斯特理论所推导出的最小值高很多的频率采样,则目标频段内的量化噪声下降。

图1显示了不同采样频率下的量化噪声密度示例。

图1.不同采样频率下,频率范围内的量化噪声密度。

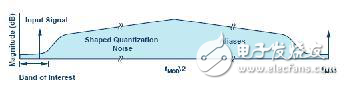

一般而言,对于特定的目标频段,每2个过采样系数就会使动态范围改善3 dB(假定为白噪声频谱)。Σ-Δ型转换器的第二个优势是噪声传递函数。它将噪声整形至更高频率(如图2所示),进一步降低了目标频段内的量化噪声。

图2.Σ-Δ噪声整形。

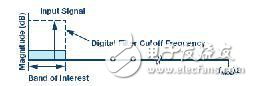

此外,Σ-Δ架构可能集成数字滤波器,用来移除目标频段外的量化噪声,实现出色的动态范围性能,如图3所示。

图3.LPF之后的量化噪声。

输入缓冲器

过采样架构的缺点之一是,相比其它采样频率较低的架构,驱动Σ-Δ型调制器的输入缓冲器要求可能会更严格。采集时间变得更短,因此缓冲器需要更高带宽。现代Σ-Δ型转换器片上集成输入缓冲器,最大程度简化使用。

此外,在检测系统中,为检测元件提供具有高精度的极高输入阻抗对于测量精度而言极为关键。这使得输入缓冲器的要求更为严格了。

本文描述了斩波容性放大器的工作原理,强调了需要放大传感器小信号至接近供电轨——比如温度测量(RTD或热电偶)和惠斯登电桥——时,此架构的优势。

Σ-Δ型模数转换器(ADC)广泛用于传感器具有较小输出电压范围和带宽的应用中(比如应变计或热敏电阻),因为这种架构提供高动态范围。具有高动态范围是因为,相比其它ADC架构,它具有低噪声性能。

Σ-Δ型转换器基于两条原理工作:过采样和噪声整形。当ADC对输入信号进行采样时,独立于采样频率的量化噪声会在直到采样频率一半的整个频谱内扩散。因此,如果输入信号以比奈奎斯特理论所推导出的最小值高很多的频率采样,则目标频段内的量化噪声下降。

图1显示了不同采样频率下的量化噪声密度示例。

图1.不同采样频率下,频率范围内的量化噪声密度。

一般而言,对于特定的目标频段,每2个过采样系数就会使动态范围改善3 dB(假定为白噪声频谱)。Σ-Δ型转换器的第二个优势是噪声传递函数。它将噪声整形至更高频率(如图2所示),进一步降低了目标频段内的量化噪声。

图2.Σ-Δ噪声整形。

此外,Σ-Δ架构可能集成数字滤波器,用来移除目标频段外的量化噪声,实现出色的动态范围性能,如图3所示。

图3.LPF之后的量化噪声。

输入缓冲器

过采样架构的缺点之一是,相比其它采样频率较低的架构,驱动Σ-Δ型调制器的输入缓冲器要求可能会更严格。采集时间变得更短,因此缓冲器需要更高带宽。现代Σ-Δ型转换器片上集成输入缓冲器,最大程度简化使用。

此外,在检测系统中,为检测元件提供具有高精度的极高输入阻抗对于测量精度而言极为关键。这使得输入缓冲器的要求更为严格了。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章