资料下载

×

基于CPLD的字形编码电路和扫描驱动电路的设计

消耗积分:0 |

格式:rar |

大小:0.1 MB |

2017-12-05

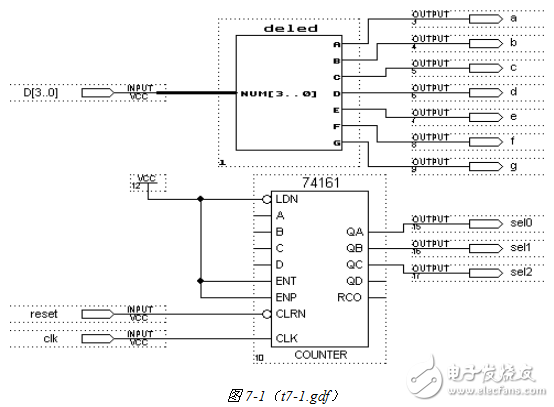

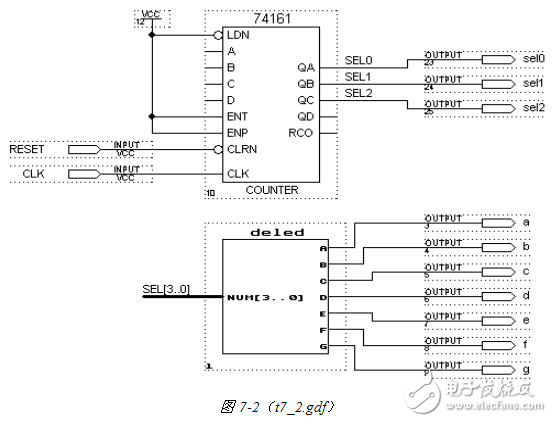

实验原理

四位拨码开关提供8421BCD码,经译码电路后成为8段数码管的字形显示驱动信号a,b,c,d,e,f,g。扫描电路通过可调时钟输出片选地址SEL[2..0]。由SEL[2..0]和a,b,c,d,e,f,g决定了8位中的那一位显示和显示什么字形。SEL[2..0]变化的快慢决定了扫描频率的快慢。

1、参考电路:如图7-1所示(时钟频率》40Hz)

2、参考电路:如图7-2所示(时钟频率《2Hz)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章