资料下载

×

高速数字电路设计之串音分析

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-12-06

由于目前大部分的数字电路中,要求时序控制时间已达到 psec 的范围。因此,在这些系统中,各种组件相互链接的导体不应再只被看作是一根简单的导线,而应将视之为呈现了高频效应的传输线。如果这些传输线没有经过合理的设计,而仍然以低频的角度来看待这些传输线,那么它们将破坏讯号的完整性(Signal Integrity;SI),而却无法分析之。

就以计算机内部中央处理器(CPU)的速度来说,目前P4的中央处理器的速度约达到3.0 GHZ左右。试想,如此高速的频率,相对所产生的传输线效应一定更为显著,因此在设计时就需更加的注意。当电路的处理效能达到高速阶段时(所谓高速是以其讯号的上升时间与导线的长度来做判断),其传输线高频的效应便会呈现出来,开始有了种种电气特性上的问题,例如:导线上的传输延迟、特性阻抗的改变、阻抗不匹配所产生的反射、导线间耦合所产生的串音等等。

基于上述的种种传输线高频效应,会破坏数字信号的完整性,使电路产生误动作,因此在设计电路之前,若能对高速数字电路设计有所了解,便可免除日后Debug的程序,且提高工作效率,相对的也降低了所需的成本,一举数得。

本文将针对高速数字电路设计(High-Speed Digital System Design)中最常见的串音噪声作一分析与探讨。

串音机制

「串音」常普遍的被考虑其对信号的影响在两导线之间会有哪些噪声的干扰,就是指一条导线上的能量耦合到其他导线上。它是由导线上通以信号所引起的电磁场交互作用而产生的;包括芯片(Chip)内部、PCB(Printed Circuit Board)板、链接器(Connector)、芯片封装,以及通信电缆中,都可能出现。而随着技术的发展,消费者对产品的要求越来越倾向于小而快,在这种情况下,就必须更加注意数字电路系统中的串音现象;因此为了避免和减小这些串音,学习并了解串音的原理和如何在设计中避免这些现象的发生就显得相当重要。

过度的导线耦合,即串音噪声过大时,将造成不良的影响有:

1.改变信号的完整性

2.改变传输线的时序(timing)

3.改变传输线的特性阻抗。

针对以上所提的串音问题,可以利用SPEED2000或是HSPICE进行时域模拟与分析,观察其在电路板上的电气特性行为。

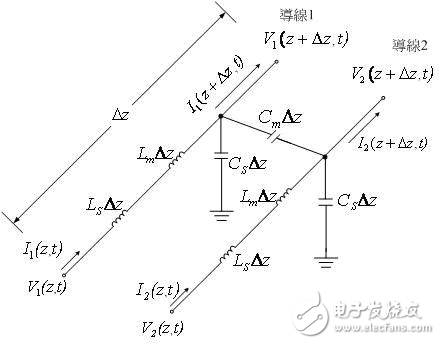

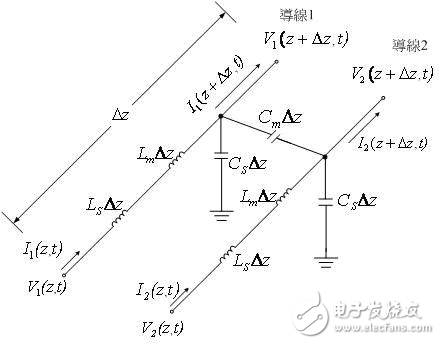

图1.1为两耦合导线间的等效电路架构,导线1代表干扰线、导线2代表受扰线。在此已考虑了传输线效应,所以可用离散模型以一个( )LC网络来描述耦合传输线的结构,实际上等效电路应包含R、L、G、C四个组件,但因此处暂不考虑传输线损耗的情形下,所以只需考虑L、C两组件即可。值得注意的地方是整条传输线应是由不断延伸多对的LC网络所组合而成的,并非只有一段L、C电路( 此方式有一个要素就是每个LC网络的导线延迟时间须远小于信号的波长或是上升时间 )。由图可看出两耦合导线间的等效电路中存在着互感(Lm)、自感(Ls)、互容(CM)与自容(Cs)。

图1.1 耦合导线间的等效电路架构

就以计算机内部中央处理器(CPU)的速度来说,目前P4的中央处理器的速度约达到3.0 GHZ左右。试想,如此高速的频率,相对所产生的传输线效应一定更为显著,因此在设计时就需更加的注意。当电路的处理效能达到高速阶段时(所谓高速是以其讯号的上升时间与导线的长度来做判断),其传输线高频的效应便会呈现出来,开始有了种种电气特性上的问题,例如:导线上的传输延迟、特性阻抗的改变、阻抗不匹配所产生的反射、导线间耦合所产生的串音等等。

基于上述的种种传输线高频效应,会破坏数字信号的完整性,使电路产生误动作,因此在设计电路之前,若能对高速数字电路设计有所了解,便可免除日后Debug的程序,且提高工作效率,相对的也降低了所需的成本,一举数得。

本文将针对高速数字电路设计(High-Speed Digital System Design)中最常见的串音噪声作一分析与探讨。

串音机制

「串音」常普遍的被考虑其对信号的影响在两导线之间会有哪些噪声的干扰,就是指一条导线上的能量耦合到其他导线上。它是由导线上通以信号所引起的电磁场交互作用而产生的;包括芯片(Chip)内部、PCB(Printed Circuit Board)板、链接器(Connector)、芯片封装,以及通信电缆中,都可能出现。而随着技术的发展,消费者对产品的要求越来越倾向于小而快,在这种情况下,就必须更加注意数字电路系统中的串音现象;因此为了避免和减小这些串音,学习并了解串音的原理和如何在设计中避免这些现象的发生就显得相当重要。

过度的导线耦合,即串音噪声过大时,将造成不良的影响有:

1.改变信号的完整性

2.改变传输线的时序(timing)

3.改变传输线的特性阻抗。

针对以上所提的串音问题,可以利用SPEED2000或是HSPICE进行时域模拟与分析,观察其在电路板上的电气特性行为。

图1.1为两耦合导线间的等效电路架构,导线1代表干扰线、导线2代表受扰线。在此已考虑了传输线效应,所以可用离散模型以一个( )LC网络来描述耦合传输线的结构,实际上等效电路应包含R、L、G、C四个组件,但因此处暂不考虑传输线损耗的情形下,所以只需考虑L、C两组件即可。值得注意的地方是整条传输线应是由不断延伸多对的LC网络所组合而成的,并非只有一段L、C电路( 此方式有一个要素就是每个LC网络的导线延迟时间须远小于信号的波长或是上升时间 )。由图可看出两耦合导线间的等效电路中存在着互感(Lm)、自感(Ls)、互容(CM)与自容(Cs)。

图1.1 耦合导线间的等效电路架构

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章