资料下载

×

PWM波及SignalTap II的使用详细资料免费下载

消耗积分:0 |

格式:pdf |

大小:0.98 MB |

2018-07-27

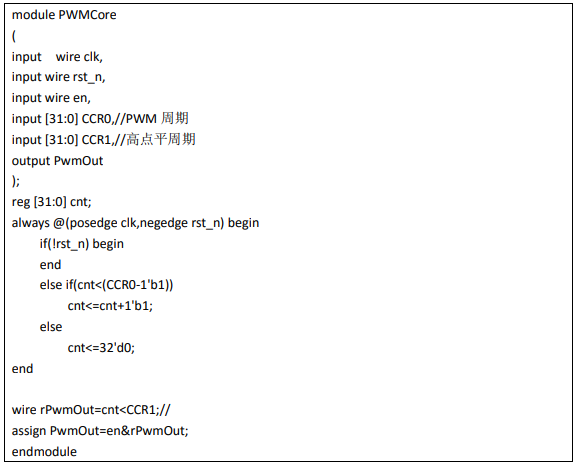

按照之前的步骤建立一个工程,然后分别建立两个 Verilog 文件,分别命名为 PWM,PWMCore,并将以下代码分别复制到 PWM.v 和 PWMCore.v 文件中。

然后将页面切换到 PWMCore.v 文件上面,利用 quartus ii 的生成例化工具生成例化文件。如图,点击生成 Verilog 语言的例化代码(注意这里也可以生成 VHDL 语言的例化文件和基于原理图的例化文件)。如果没有错误的话出现生成成功的对话框。生成的例化文件命名规则是在原有的文件名_inst,本例中的是 PWMCore_inst.v。打开文件,将例化接口复制并粘贴到 PWM.v 文件中,并进行接口的连接(注意名字的大小写和数据宽度)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章