资料下载

FE1.1s和FE2.1 USB2.0 Hub中英文使用数据手册及参考电路合集免费下载

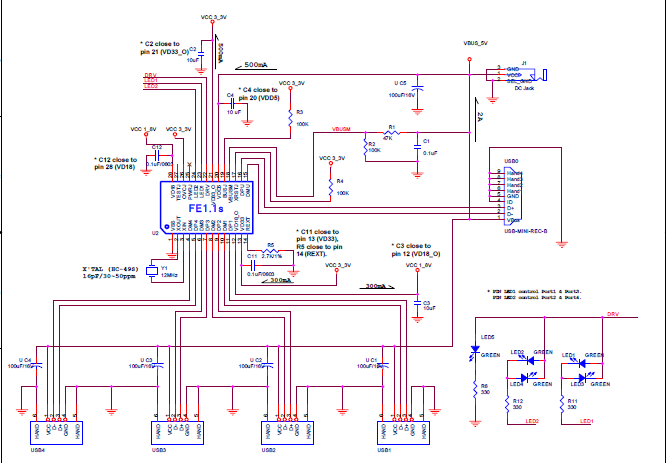

FE1.1s是高度集成, 高质量, 高性能, 低能耗, 同时还是USB 2.0 高速4端口集线的低成本解决方案。

它采用单个交换转换器 (Single Transaction Translator) (STT) 构建以便获得更多的效益。六个而不是两个非周期转换缓存以减少潜在的通信干扰。整个设计基于状态机控制,以减小响应的延迟时间;在此芯片中未使用微型控制器。

为保障高质量,整个芯片通过测试扫描链(Test Scan Chain)– 即使在高速 (480MHz)模式下,使所有的逻辑元件在装运前被充分测试。特别是内建自检(Build-In-Self-Test)模式目的在于使用所有的高速,全速,以及低速模式模拟前端端口 (AFE) 在封装和测试阶段也是如此。

低能耗的实现是通过使用0.18μm 技术以及集成的电源/时钟控制机制。大部分引脚不需要计时,除非被用到。

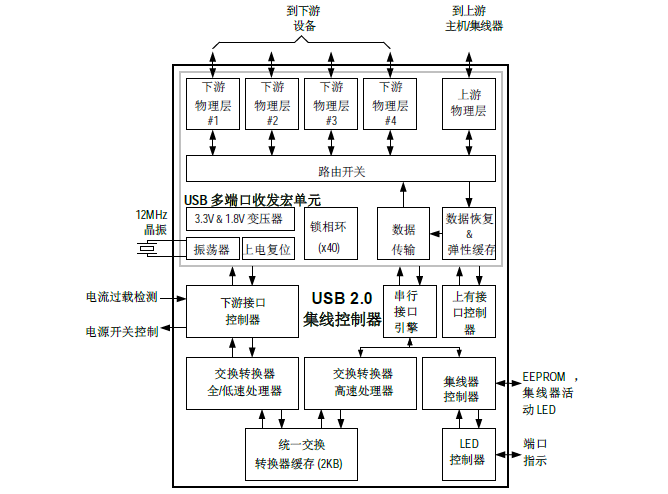

FE2.1芯片是高度集成,高品质,高性能,低能耗,总体花费低的高速七端口USB2.0集线器解决方案。

FE2.1适应多样任务译码器(MMT)风格,借此达到最大的数据输出。六个(而不是两个)非周期数据处理缓冲器被用来将潜在的传输干扰降至最低。整个设计基于状态机控制原理,降低了相应延迟时间。该芯片中没有使用微控制器。

为了保证高品质,整个芯片覆盖测试扫描链—包括高速模块(频率480MHz),所以在运行前可以检测所有逻辑组件。芯片拥有特殊的自检建立模式,可以在封装和测试阶段测试高速、全速和低速模拟前端结束(AFE)元件。

通过使用0.18微米制造工艺和全面电源/时钟控制机制实现低功耗。若无必要,芯片的大部分不会被锁住。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

-

Christian777

2021-08-24

0 回复 举报需要汤铭的第一手资料 找我呀 15013641220 收起回复

Christian777

2021-08-24

0 回复 举报需要汤铭的第一手资料 找我呀 15013641220 收起回复

-

lequsshow

2021-07-30

0 回复 举报hub挂了,烧毁得完全看不出来芯片型号,参考一下原理图, 收起回复

lequsshow

2021-07-30

0 回复 举报hub挂了,烧毁得完全看不出来芯片型号,参考一下原理图, 收起回复

- 相关下载

- 相关文章