资料下载

×

FPGA视频教程之时序分析基础的详细资料说明

消耗积分:0 |

格式:rar |

大小:0.00 MB |

2019-03-05

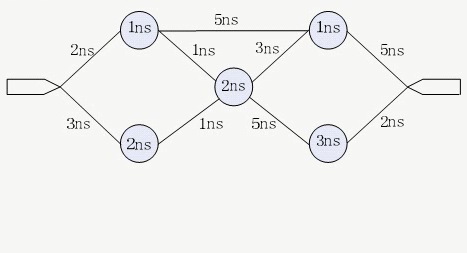

第二阶段是一种功能强大的再分配式计时,它使用标准约束、分析和报告方法对您设计中的所有逻辑进行计时。在您设计的所有定时路径中,使用II级时序的GUI或命令行界面对所有时序路径进行重新划分、分析和报告结果。在运行II级非标准时序之前,您必须指定描述时钟特性、定时异常、以及相应的到达和时间的约束条件。您可以使用GUI或命令(命令),以高级设计约束(UnitedDesignContractions,简称DesignConstraits,简称二是再接逻辑的再分配,以满足要求。

在时序分析过程中,第二阶段对设计中的路径进行了分析,对各路径上的传播延迟进行了分析,检查了各路径上的传播延迟,并在控制台窗格中的报告中以松弛的形式对时序结果进行了检测。如果再转制时机报告违章行为,则可以自定义报告查看精确的计时特定路径,然后再对这些路径进行修正。设计是无时序冲突的,您可以确信逻辑符合目标设备的意图。这是一个完整的静态时序分析工具,您可以使用标记工具对产品进行再加工和再加工。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章