资料下载

Cadence的详细资料简介

Cadence 16.6电路设计与仿真从入门到精通

内容指南

Cadence为挑战简短、复杂、高速芯片封装设计,推出了以Windows XP的操作平台为主的Cadence SPB 16.6。

本章将从Cadence的功能特点及发展历史讲起,介绍Cadence SPB 16.6的安装、界面、使用环境,以使读者能对该软件有一个大致的了解。

知识重点

· Cadence简介

· Cadence软件的安装

· Cadence SPB 16.6的启动

1.1 Cadence简介 方块

Cadence公司在EDA领域处于国际领先地位,旗下PCB设计领域有市面上众所周知的OrCAD和Allegro SPB两个品牌,其中OrCAD为20世纪90年代的收购品牌。Allegro SPB为Cadence公司自有品牌,早期版本称为Allegro PSD。经过10余年的整合,目前Cadence PCB领域仍执行双品牌战略,OrCAD覆盖中低端市场(以极低的价格就可以获得好用的工具,主要与Protel和Pads竞争),Allegro SPB覆盖中高端市场(与Mentor和Zuken竞争)。

(1)OrCAD涵盖原理图工具OrCAD Capture、Capture CIS(含有元件库管理之功能),原理图仿真工具PSpice(PSpiceAD、PSpiceAA),PCB Layout工具OrCAD PCB Editor(Allegro L版本,OrCAD原来自有的OrCAD Layout在2008年已经全球范围停止销售),信号完整性分析工具OrCAD Signal Explorer(Allegro SI基础版本)。

(2)Allegro SPB涵盖原理图工具Design Entry CIS(与OrCAD Capture CIS完全相同)、Design Entry HDL(Cadence旧Concept HDL),原理图仿真工具Allegro AMS Simulator(即PSpiceAD、PSpiceAA),PCB Layout工具 Allegro PCB Editor(有L、Performance、XL、GXL版本),信号完整性分析工具Allegro PCB SI(有L、Performance、XL、GXL版本)。

(3)Cadence 16.6与之前的几个版本在功能模块上既有相同的地方,也有不同之处,下面对比图1-1所示的启动菜单简单介绍一下具体功能模块。

· Design Entry CIS:Cadence公司收购的OrCAD公司的旧版本Capture和Capture CIS,是国际上通用的、标准的原理图输入工具,设计快捷方便,图形美观,与Allegro软件平台实现了无缝链接。

· Design Entry HDL:是旧版本的Concept HDL,提供了基于Design Capture环境的原理图设计,允许使用表格、原理图和Verilog HDL进行设计。

· Design Entry HDL Rule Checker:检查Design Entry HDL规则的工具。

· Library Explorer:包括Part Developer和Library Explorer两个功能,进行数字设计库的管理,可以调用建立Part Developer、PartTable Editor、Design Entry、Packager-XL和Allegro的元件符号和模型的工具。

· OrCAD Capture:原理图设计工具。

· OrCAD Capture CIS:原理图设计工具。

· Package Designer:高密度IC封装设计和分析。

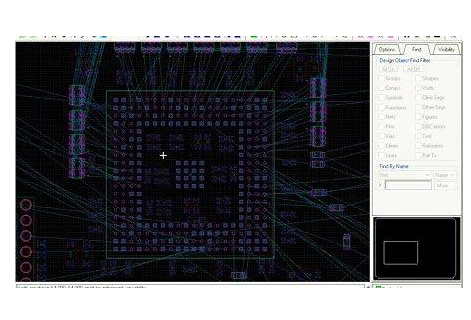

· PCB Editor:完整的PCB设计工具。

· PCB Router:CCT布线器。

· PCB SI:建立数字PCB系统和集成电路封装设计的集成高速设计和分析环境,可以解决电器性能相关问题,如信号完整形、串扰、电源完整性和EMI。

· Physical Viewer:Allegro浏览器模块。

· Project Manager:Design Entry HDL的项目管理器。

· PSpiceAD:原理图仿真工具。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章