评估低抖动PLL时钟发生器的电源噪声抑制

TD-SCDMA RD V2.1设计满足Rx屏蔽掩模和灵敏度要求

防止MAX2104电路中的寄生模式振荡

基于28nm工艺制程的7系列FPGA

为高速数据转换器设计低抖动时钟

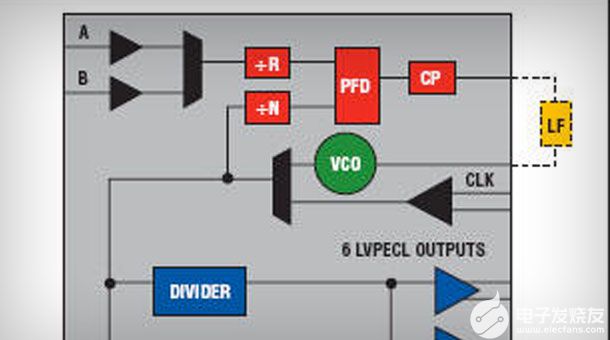

pll频率合成器工作原理与pll频率合成器的原理图解释

ADF4007BCPZ高频分频器/PLL频率合成器概述

使用MAX9382的锁相环应用

锁相环的基本组成、工作原理及应用

如何在PLL输出端产生最低的相位噪声?

一文简析TC3xx Rest/Clock/Watch模块

如何轻松选择合适的频率发生组件

pll锁相环版图设计注意

DC精确滤波器简化了PLL设计

微波频率合成器提供多倍频程覆盖范围和出色的相位噪声性能

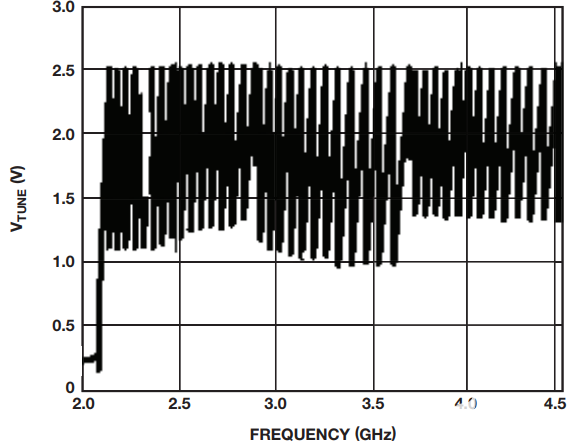

使用具有精密相位控制的超宽带PLL/VCO用硅代替YIG调谐振荡器

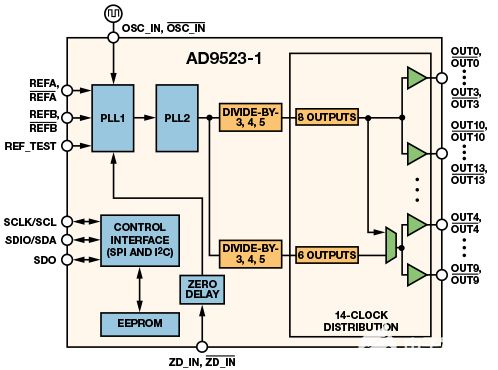

双环路时钟发生器清除抖动,提供多个高频输出

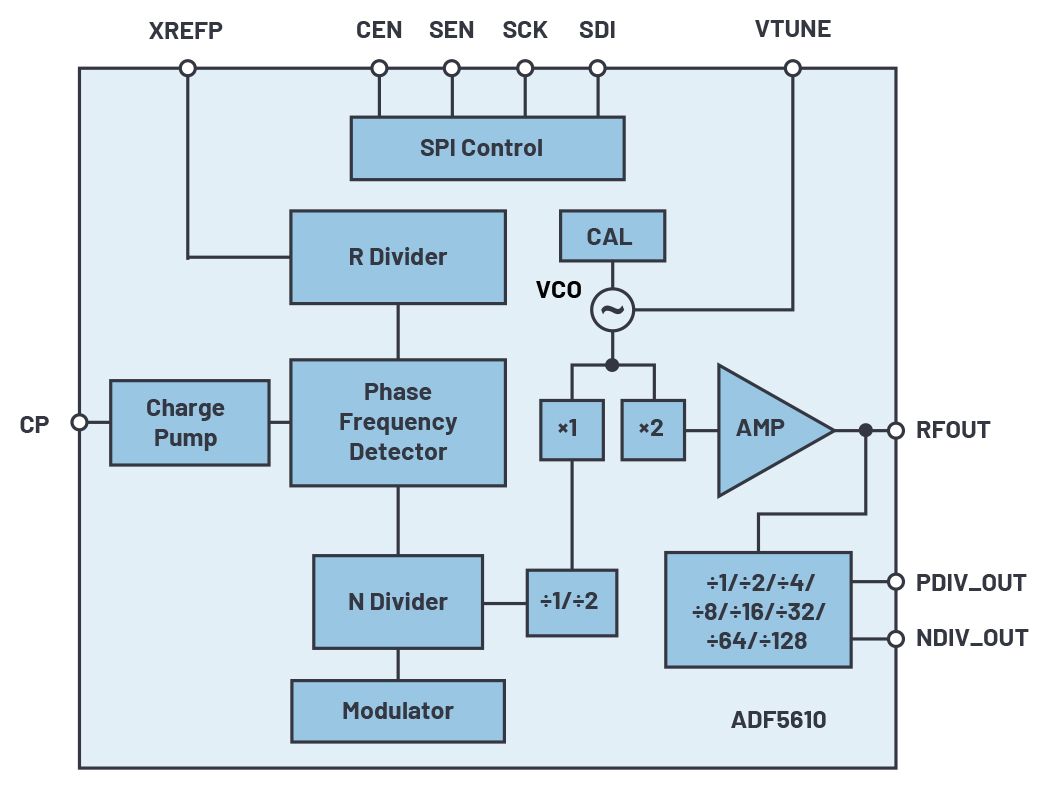

设计带有新型宽带整数N分频PLL频率合成器的直接6GHz本振

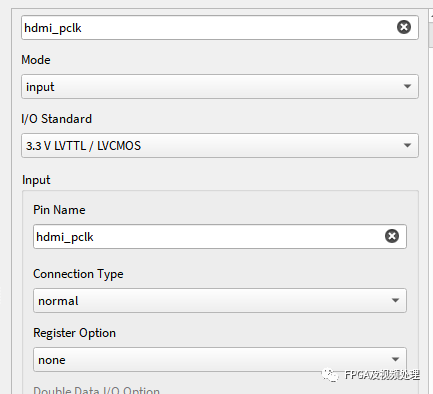

在Trion上驱动PLL走pllin管脚

具有14通道分配功能的单芯片时钟发生器解决了网络中的时序挑战