资料下载

×

基于EP2C35的DSP阵列板通信接口设计与实现

消耗积分:0 |

格式:rar |

大小:0.36 MB |

2017-10-19

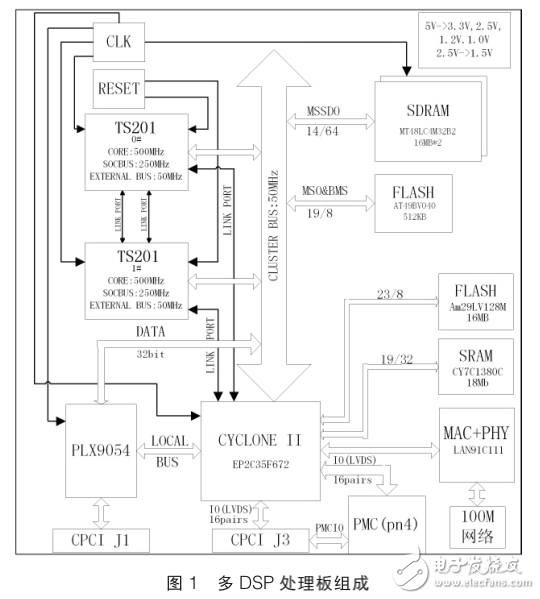

DSP 阵列板采用两片 ADI 公司的 TS201 浮点型 DSP 作为

处理核心,和一片 CYCLONE II 系列 EP2C35 FPGA 作为计算

处理阵列对外扩展的控制部件 , 它一方面实现处理阵列的

CLUSTER BUS 和 CPCI 背板的 PCI 总线之间的转接(与 9054

协作),另一方面实现 Link PORT 和百兆网口之间的异步通讯,

基于此,对外提供标准 CPCI 总线接口,可与 CPCI 外围总线模

块配合使用,对外提供一个 100M 以太网。 同时板载 SDRAM 和

Flash 存储设备,整板可持续对外提供强大的定点和浮点运算能

力,可应用于持续、高强度的复杂运算场合,尤其是典型数字信

号处理算法。 其组成见图 1。

TS201 的外部接口功能并不丰富,只有 ADI 公司自定义的

CLUSTER BUS 和 Link 口,这两种接口的带宽能达到 5GB / S,

为增强其外部接口的通用性,本设计考虑将 CLUSTER BUS 转

换为 PCI 总线,将 Link 口转换成 100M 以太网口。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章