资料下载

BF3005CSP型VGA CMOS图像传感器的设计指南资料详细说明

本文档的主要内容详细介绍的是BF3005CSP型VGA CMOS图像传感器的设计指南资料详细说明。

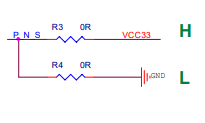

注:下面所述的电压值都为典型值,各电压的取值范围可参看 BF3005 CSP Datasheet。 2.1 电源地设计 ¾ BF3005 芯片分四路电源:VDDIO = 1.7V~3.3V,VDD3A = 3.3V, VLDO= 3.3V,VDDD=1.5V。 ¾ 设计模组时电源方案应注意: ¾ 应尽量保证 VDD3A 电源质量。 ¾ VDDD 是芯片的 Core 电压,它可以由 VDDD pin 直接提供 1.5V,也可以经由 VLDO pin 输入 3.3V 电源,经过内部 LDO 产生 1.5V 电压。 ¾ VDDD 和 VLDO 不能同时供电,不用的一路可以悬空;VDDD 直接供电比 VLDO 供电,功耗会小一些。 2.2 外围应用注意事项 ¾ 设计电源模块时,一般采用的都是第一种方案;LDO 应尽可能放置在靠近芯片输入引脚处,电源线走线一般应小于等于0.15mm,最小不应该小于0.1mm;供给芯片VDD3A 的电源线要尽可能短;并且在每路电源供给芯片靠近引脚处需要分别放一0.1uF 滤波电容。 ¾ 设计地线时,分两路网络处理,VSSA(AGND) 和VSSD(DGND)要分开接;参考地线线宽为 0.1mm—0.15mm 之间,在允许布线的条件下尽可能加宽。 ¾ C1—C2 是必须的,其容值为0.1uf 的贴片电容,省略会影响图像质量; ¾ 各个电容尽可能靠近相应的引脚。并且走线应注意先经过滤波电容后再进sensor;滤波电容是推荐的,省略可能会影响图像质量; ¾ 电源走线时,不管采用那种供电方案都建议把VLDO 和VDD3A 分开走线; ¾ VCLK、XCLK、HSYNC、VSYNC 的走线之间最好采用地线屏蔽或远离; ¾ SCL、SDA、的走线应该尽量远离XCLK、VCLK、D0、D1(低位高频数据pin),或用地线屏蔽; ¾ RSTB(复位)、PWDN、VDD3A 的走线也应该尽量远离XCLK、VCLK、D0-D7; ¾ MOTION 引脚为动态检测管脚,当检测到有动态变化时,此管脚输出为高,可以外接蜂鸣器电路,不用时此引脚悬空。 ¾ I2C 走线时必须加4.7K (4.7K 是推荐值) 的上拉电阻。 ¾ 芯片的NC 引脚在布线时直接悬空不接; ¾ 如果采用有源晶振,则只有由XCLKI 输入时钟信号XCLKO悬空,如果采用无源晶振, XCLKO,XCLKL,两路都要接。 ¾ P_N_S 引脚 CCIR656 PAL、NTSC 模式选择端口,PAL:720*576;NTSC:720*480,悬空或接高电平为 PAL 输出,接地为 NTSC 输出。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章