资料下载

×

如何使用FPGA实现FIR抽取滤波器的设计

消耗积分:1 |

格式:pdf |

大小:0.10 MB |

2020-07-07

用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

具体实现

结构设计

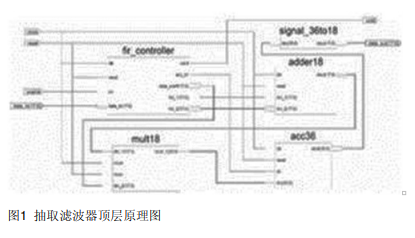

基于抽取滤波器的工作原理,本文采用XC2V1000实现了一个抽取率为2、具有线性相位的3阶FIR抽取滤波器,利用原理图和 VHDL共同完成源文件设计。图1是抽取滤波器的顶层原理图。其中,clock是工作时钟,reset是复位信号,enable是输入数据有效信号,data_in(17:0)是输入数据,data_out(17:0)是输出数据,valid是输出数据有效信号。adder18是加法器模块,mult18是乘法器模块,acc36是累加器模块,signal_36to18是数据截位器模块,fir_controller是控制器模块。控制器定时向加法器、乘法器和累加器发送数据或控制信号,实现流水线操作。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章