资料下载

×

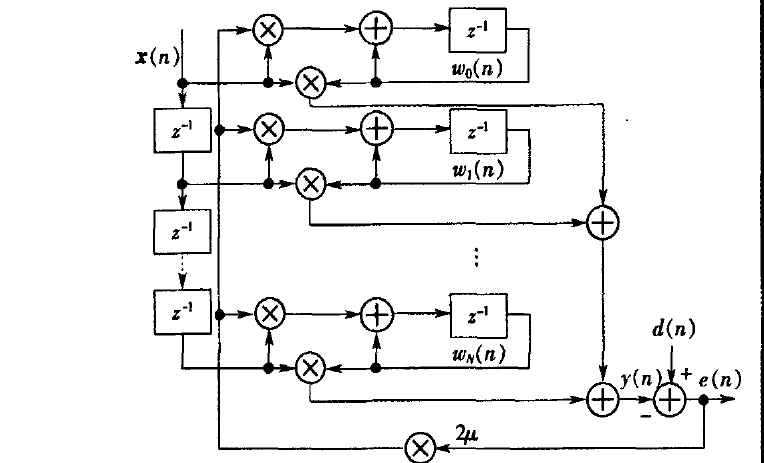

DLMS高速自适应滤波器的FPGA实现

消耗积分:0 |

格式:rar |

大小:0.33 MB |

2021-01-22

在分析传统自适应滤波算法的基础上,针对自适应滤波器的硬件实现,采用一种适合FPGA实现的DLMS算法。使用VHDL语言完成设计,仿真实验验证了设计的正确性,经过编译和布局布线后对改进算法和传统算法进行了比较,结果表明改进算法在增加硬件消耗较少的情况下有效提高了系统工作频率。

在数字信号处理中.如果待处理信号的统计特性是未知的,那么采用固定系数的滤波算法就不能有效处理信号。解决这一问题的方法是采用自适应滤波器。自适应滤波器是一种可根据环境变化调整系数的非线性滤波器,该滤波器可以只利用环境信息通过合适的自适应算法来进行在线的系数更新。相比于固定系数滤波器,它不需要事先知道需处理信号的统计特性,只用提供一个输入信号和参考信号,通过不断调整系数,使输入信号尽可能接近参考信号。由于自适应滤波器在滤波过程中是从含噪信号中减去噪声信号,因此常能获得比固定系数滤波器更高的信噪比。随着超大规模集成电路技术的发展。自适应滤波器的速度、精度得到了很大提高,在越来越多的领域中得到了广泛应用。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章