资料下载

如何使用CPLD实现出租车计费器的设计

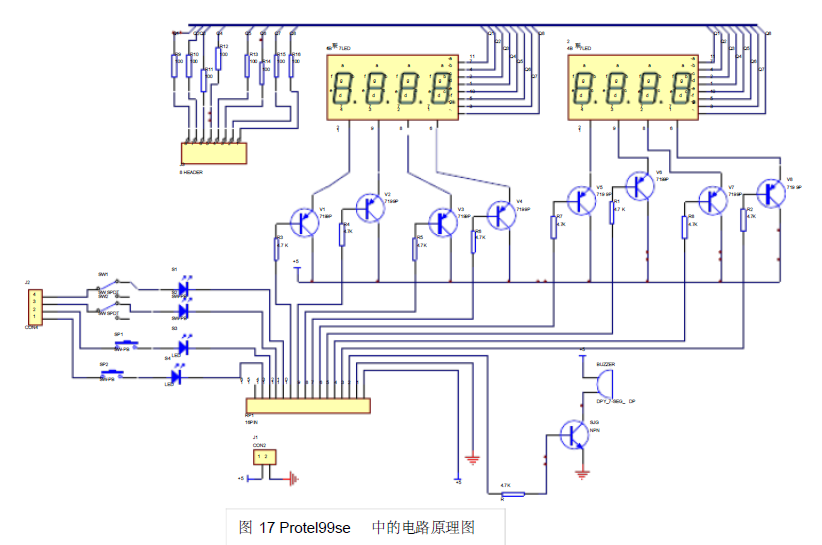

本文借助QuartusⅡ9.0软件,基于大规模可编程逻辑器件FPGA,利用Verilog HDL 语言,进行出租车计费器设计。该出租车计费系统包括计数器分频模块、数码管分频模块、计程模块、计时模块、计费模块、控制模块、数码管显示模块和顶层主控模块共八大部分;分起步、里程、等待三个阶段。该出租车计费器能够自行设定计费标准,借助CycloneⅡ系列EP20C8Q208C8N芯片的FPGA开发板,进行功能仿真,并且利用外围电路和开发板的结合,能够进行相应的硬件测试。测试结果由2片4个相连的7段共阳极数码管驱动电路来显示。

随着出租车行业的发展,对出租车计费器的要求也越来越高,用户不仅要求计费器性能稳定、计费准确;同时还要求其具有计价标准的灵活设定、营运额统计、密码设定等功能。目前,出租车行业面临油价上涨和夏季空调费调整的问题,修改计价标准随着油价的上涨势在必行,所以出租车计费器计价标准的灵活设定成为计费器不可缺少的一部分。因此性能稳定、便于检定、维护及修改参数成为出租车记费器的关键技术。出租车计价系统较多的是利用单片机进行控制,但较易被私自改装,且故障率相对较高,不易升级。而FPGA 具有高密度、可编程及有强大的软件支持等特点,所以设计的产品具有功能强、可靠性高、易于修改等特点。

随着FPGA(Field Programmable Gate Array) 等可编程器件的出现,解决了传统电子设计不能完成的任务。利用FPGA 来实现出租车计费器,可行性很高,电路简单,大大减少外围器件,可以用软件完全仿真,灵活度高,而且编好的系统可以在不同的FPGA 芯片上通用。同时由于FPGA 的功能完全取决于语言Verilog HDL 编写的程序,不拘泥于某种芯片的特殊指令 ,更加提高了产品的更新换代能力。FPGA 在电子设计领域中价格低廉, 有良好的发展趋势, 它的出现必定会占领大部分数字器件市场。

本设计选用的FPGA 芯片,主要是Altera 公司的CycloneⅡ 系列芯片EP20C8Q208C8N。使用软件QuartusⅡ9.0 和超高速硬件描述语言Verilog HDL ,从而实现计价标准的灵活设定。使得该出租车计费器的特点是计费准确、性能稳定、分阶段(起步、里程、等待)自动计费。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章