资料下载

×

FPGA设计与验证

消耗积分:0 |

格式:rar |

大小:2.85 MB |

2020-09-01

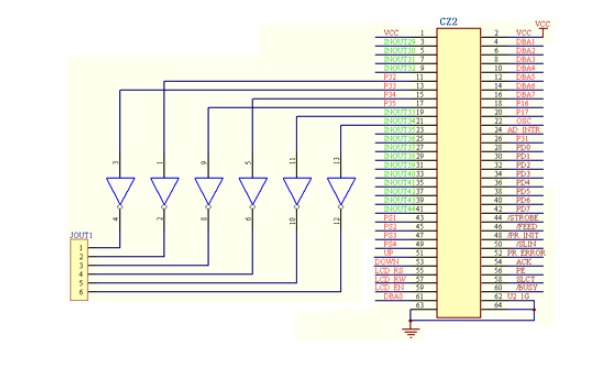

该实验箱包含两部分,一部分为系统底板,包含主要的功能扩展;另一部分是包含CPLD或FPGA器件的子板。结构釆用模块化设计思想,在地板上划分为从AZ以及AAQQ的功能模块,一共有42个,有些部分不可用,有些只是演示性的,主要如下所示十进制BCD码显示区实验模块(A16×16点矩阵显示实验模块(B)模数转换ADC0809实验模块(C);执行机构实验区包括直流电机和步进电杋及配套的驱动电路等实验模块(D)PS2键盘和鼠标实验模块(E)时钟源模块可产生0.5~100MHz时钟信号分三组独立提供(F);RS232串行通信实验模块(G);负压发生模块及电机驱动电路模块(H)常用含段驱动和位译码驱动数码管显示实验模块(Ⅰ);USB通信接口实验模块(J);2×64PIN通用接口实验模块,可配接FPGA/CPLD/DSP/SOPC/ARM/单片机竞赛板及其它各种适配板等(K)常用信号输入输岀实验模块,可实现微型打印杋,液晶显示及常用数据信号的控制等

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章