资料下载

实现高速复用数模转换器同步的方法详细说明

概述

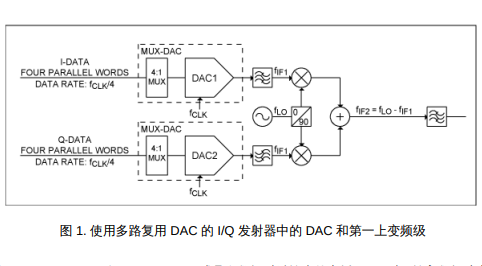

在很多发射应用中必须产生多路相对相位准确已知的模拟输出。在正交调制器中(图 1),I 和 Q 通道必须具有明确的相位关系来实现镜频抑制。图 1 中,DAC1 和 DAC2 的延迟必须匹配。使用数字波束成形技术的发射器需要准确地控制大量 DAC 之间的相对相位。

使用具有多路输入的 DAC (MUX-DAC)如 MAX19692,或具有数据时钟输出的内插 DAC 时,输入数据速率为 DAC 刷新速率的 1/N,DAC 在一个或两个数据时钟跳变沿锁存数据。MAX19692 中 N = 4,输入数据速率为 DAC 刷新速率的 1/4。DAC 输出一个由输入时钟经数字分频得到的数据时钟(DATACLK)。DAC 上电时,数字时钟分频器可在 N 个状态的任意一个启动。如果使用多个 DAC,不同 DAC 的时钟分频器会在不同的状态启动,所以 DAC 会在不同的时间锁存数据。除非这种情况被发现并校正,否则不同的 DAC 输出数据时相互之间可能会有一个或更多个时钟周期的延迟。如果每个 DAC 的时钟分频器可以复位,那么这种情况可以避免,但是仍然会存在一些问题。如果其中一个时钟分频器发生错误,DAC 会变得永久异相,除非执行一些错误状态检测方法。为了保证系统的可靠性,必须检测相位错误状态并改正。如果 DAC 工作于非常高速的状态下,那么复位信号与输入时钟的同步也可能是个难题。图 2 所示是 MAX19692 的时钟(CLKP,CLKN)和数据时钟(DATACLKP,DATACLKN)接口的简化框图。初始时钟由一个两位计数器四分频后用于锁存数字 DAC 输入。该计数器可能在四个状态中的任意一个启动(图 3)。如果使用两个多路复用 DAC,这两个 DAC 可能会在不同的状态启动。这可能导致 DAC1 的锁存与 DAC2 的锁存之间存在 -1、0、1 或 2 个时钟周期的延迟。 MAX19692 的数据时钟输出再由数据输入锁存时钟进行 2 分频或 4 分频。然后数据在双倍数据率(DDR)模式下在时钟的两个跳变沿进行锁存,或者在四倍数据率(QDR)模式下在时钟的每 90°相位处进行锁存。如果多个 DAC 的数据时钟延迟相匹配,或数据时钟相互之间反相,那么锁存时钟相匹配。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章