资料下载

FPGA器件如何配置电平和接口标准

Virtex-4、Virtex-5和Spartan-3系列器件增加和修改了一些与配置有关的专用引脚,这些专用引脚如下。

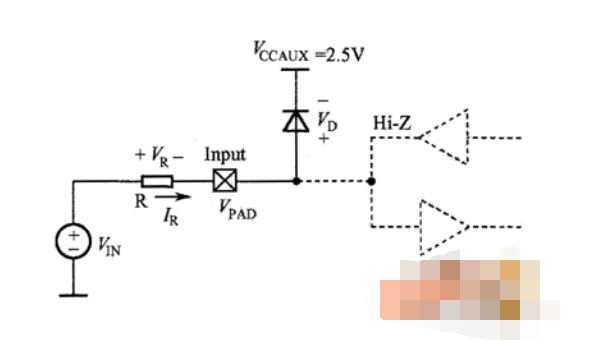

(1)VCCAUX辅助电源:在Virtex-4、Virtex-5、Spartan-3及Spartan-3E器件中,Vccaux为2.5 V;在Spartan-3A及Spartan-3ADSP中,Vccaux可以是2.5 V或是3.3 V;在Spartan-3AN中,Vccaux是3.3 Y。

(2)专用控制信号HSWAP EN脚:当HSWAP EN为低时,在配置期间所有用户输入/输出(I/0)脚将被上拉(Pull-Up)。默认值为高(内部上拉),即配置期间关闭用户I/O脚的内部上拉功能。

(3)配置时钟(CCLK)引脚:CCLK引脚根据配置模式的不同,既可以是输入,也可以是输出。

(4)配置完成状态输出(DONE):当DONE为高时,表示成功完成配置;否则为配置失败。DONE引脚通常需要外部上拉电阻,上拉电阻的大小与所需的驱动电流有关,一股情况下为330Ω。

(5)允许配置或配置复位(PROG_B)信号:低电平有效,即当将该引脚拉低后,将复位内部的配置寄存器;当恢复高电平时,开始配置,直到DONE为高结束配置。

(6)模式控制引脚MO、M1及M2:决定FPGA的配置模式。

(7)边界扫描模式信号引脚:包括数据输入脚(TDI)、数据输出(TDO)、状态和控制(TMS),以及JTAG方式配置时钟(TCK)。

这些专用配置和边界扫描引脚在Virtex-4和Vitex-5的器件中由VCC00供电,在Spartan-3中用VCCAUX辅助电源为这些信号脚提供电源,所以这些配置引脚的上拉应该对应拉到对应的VCCO0和VCCAUX。这些专用配置引脚只能用于器件的配置,不能用于其他目的。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章