资料下载

×

如何使用FPGA实现高吞吐量低存储量的LDPC码译码器

消耗积分:0 |

格式:rar |

大小:0.45 MB |

2021-02-03

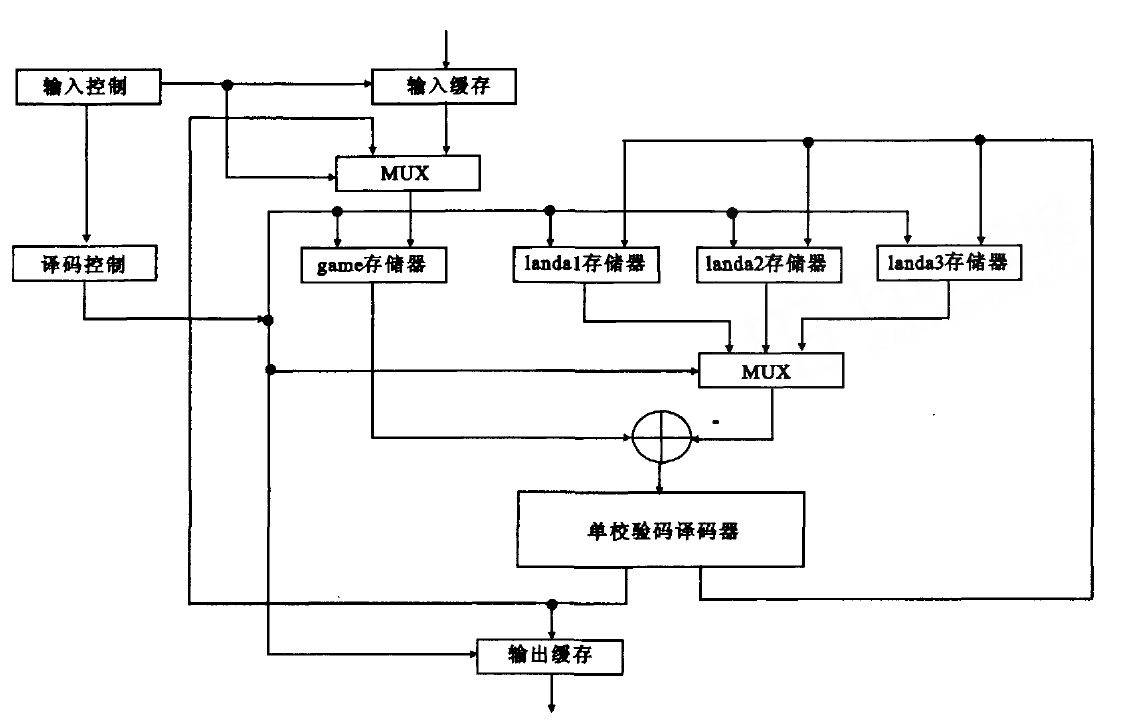

针对一类规则(r,c)-LDPC(low-density parity check)码,提出了一种基于Turbo译码算法的高吞吐量存储器效率译码器。与传统的和积译码算法相比,Turbo译码算法对多个分组进行并行译码,每个分组采用并行结构进行译码,具有更快的收敛速度和更少的存储空间。为了对一个具有并行结构的数据包进行解码,首先将LDC码分为若干个超码。然后用并行BCJR算法对每个超码进行解码。为了进一步简化算法的内部结构和复杂度,提出了一种改进的陪集算法。基于Altera Stratix EP1S25 FPGA器件,开发了一种包含15个并行译码器的FPGA芯片,用于长度为1600的规则(r,c)-LDPC码,可并行解码3个数据包,通过20次解码迭代可达到50Mbit/s的吞吐量。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章