资料下载

×

如何使用FPGA实现跳频系统中的Turbo码译码器

消耗积分:0 |

格式:rar |

大小:0.27 MB |

2021-04-01

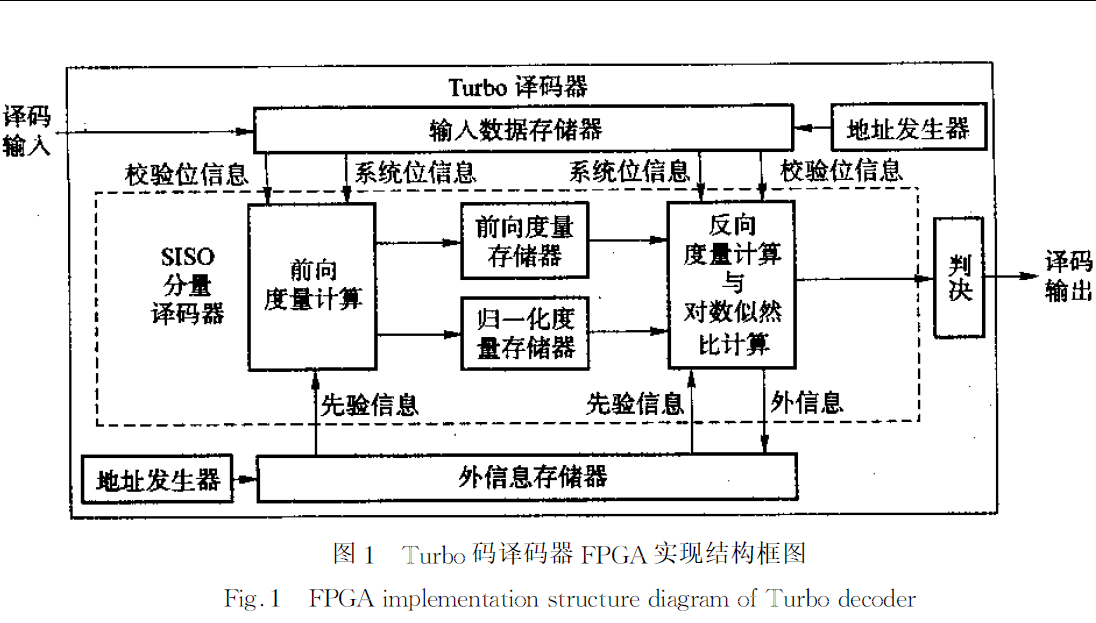

给出了跳频系统中 Turbo码译码器的FPGA( field programmable gate array)实现方案。译码器采用了MaxLog-map译码算法和模块化的设计方法,可以对不同帧长的 Turbo码进行译码。在Xinx公司的FPGA芯片xc3s20004g676上实现了帧长可变的Tunb译码器。在帧长为1024lit、迭代5次条件下,该译码器时延为0.812ms数据吞吐量为1.261Mbit/s.分别在高斯白噪声和部分频带噪声干扰两种信道环境中测试该ˆurbo码译码器的误码率性能,在部分频带噪声干扰中使用了A(α(自动増益控制),结果表明,A(C有效提高了译码器在部分频带噪声干扰下的性能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(1)

发评论

-

chenlance2979

2021-05-31

0 回复 举报承接fpga和芯片开发项目, 免费分享技术资料2T云盘, +VX: www8928 收起回复

chenlance2979

2021-05-31

0 回复 举报承接fpga和芯片开发项目, 免费分享技术资料2T云盘, +VX: www8928 收起回复

- 相关下载

- 相关文章