信号回沟,即波形边缘的非单调性,是时钟的大忌,尤其是出现在信号的门限电平范围内时,由于容易导致误触发,更是凶险无比。所以当客户测试发现时钟信号回沟,抱着一心改板的沉痛心情找到高速先生时,高速先生丝毫不敢大意,一番分析确认之后,给出的答复却让客户喜出望外:测试点的时钟回沟是真实存在的,但是芯片得到的时钟信号质量却没有问题,简而言之,单板的时钟信号没问题,可以放心使用。

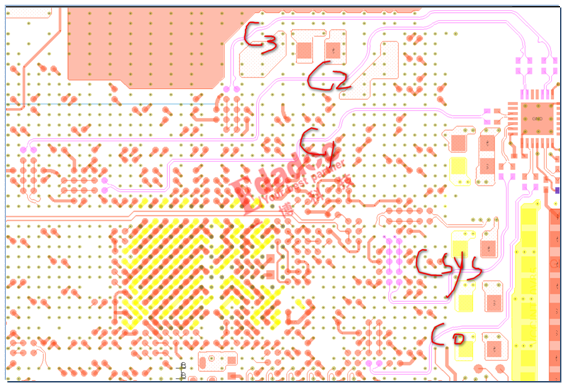

其实,高速先生刚拿到单板时心里也没底,因为时钟信号频率并不算低,有 400MHz,而且针对 5 路时钟信号的设计查板也并未发现异常。

仿真初始阶段,为了确认模型的准确性,首先对客户提供的测试点上的波形进行了仿真拟合,以 C0 通道时钟为例,仿真波形的回沟如约而至,与测试波形的延时、回沟的位置基本一致,说明仿真建模没有问题,看到这样的结果,客户的心开始下沉:回沟得到了仿真验证,这回没得救了。

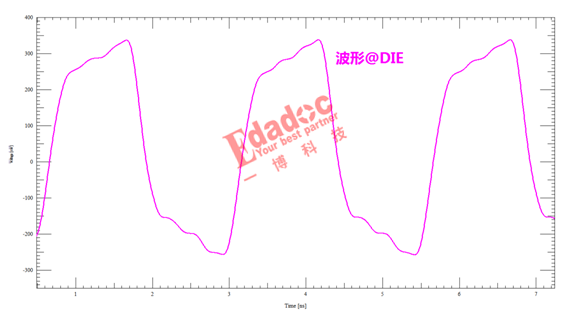

高速先生感觉可以再抢救一把,因为最关键的芯片 DIE 上的时钟波形还没看到,还有一线生机。怀着忐忑的心情,高速先生按下了“Simulation”键,随着 DIE 上的波形在屏幕上渐次展开,高速先生松了口气,芯片上的时钟回沟神奇的消失了!

看到这样的结果,客户既喜且疑,喜的是芯片上的时钟信号正常,疑的是测试点明明就在芯片背面的过孔处,为何测试得到的时钟波形会与芯片 DIE 上的天差地别?

测试最尴尬的莫过于“所测非所得”,出现这种情况,很多时候与测试点的位置选择有关,比如本案例:看起来芯片背面的过孔似乎距离芯片最近,最能反映芯片接收信号的真实情况,其实不然,我们最终需要关注的是芯片 DIE 上的信号,而芯片的 DIE 与 PIN 之间还隔着千山万水——芯片内部封装布线,尤其是封装较大的 BGA 芯片,封装布线的影响更加明显,这也是很多芯片会提供封装补偿(Pin-delay)的原因