资料下载

×

宽带数字信道化接收机的FPGA实现

消耗积分:10 |

格式:rar |

大小:1 MB |

2011-03-07

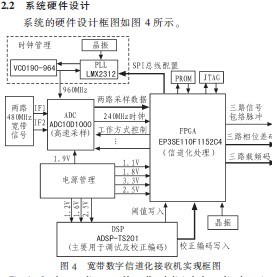

为解决现代电子战对接收机处理带宽宽、灵敏度高及实时性处理的要求,提出一种数字信道化接收机的设计方法。在推导高效信道化接收机模型的基础上,采用多相滤波器结构实现的数字信道化接收机。该接收机利用超高速A/D对数据进行高速采样,然后由高性能FPGA进行数据抽取、多相滤波、CORDIC算法等信道化实时处理。为了提高实时性,采用并行IFFT实现。该信道化接收机不仅能稳定输出载频及相位信息,还能处理三路同时到达的不同信号。实际的性能测试结果表明该接收机的功能正确并达到预定指标。

- Abstract:

- To meet requirements of the modern electronic warfare on the wide receiver processing bandwidth, high sensitivity and real-time processing,a digital channelized receiver design was proposed. Based on the derivation of efficient channel receiver model,polyphase filter structure wa adopted to realize digital channelized receiver. The high-speed A/D was used for data acquisition,and high-performance FPGA exceeded the channel real-time processing such as data extraction, polyphase filter, and CORDIC algorithms. In order to improve real-time, parallel IFFT was implemented. The receiver not only could steadily output the frequency and phase information,but also could deal with three different ways signals which arrived at the same time. The actual performance results show that the receiver has correct function and hits the intended target.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(2)

发评论

-

h1654155781.4660

2012-09-10

0 回复 举报好东西 收藏了!! 收起回复

h1654155781.4660

2012-09-10

0 回复 举报好东西 收藏了!! 收起回复

-

chuyanliang

2011-08-01

0 回复 举报不错!!!!!!!!!!!!!!!! 收起回复

chuyanliang

2011-08-01

0 回复 举报不错!!!!!!!!!!!!!!!! 收起回复

- 相关下载

- 相关文章