资料下载

×

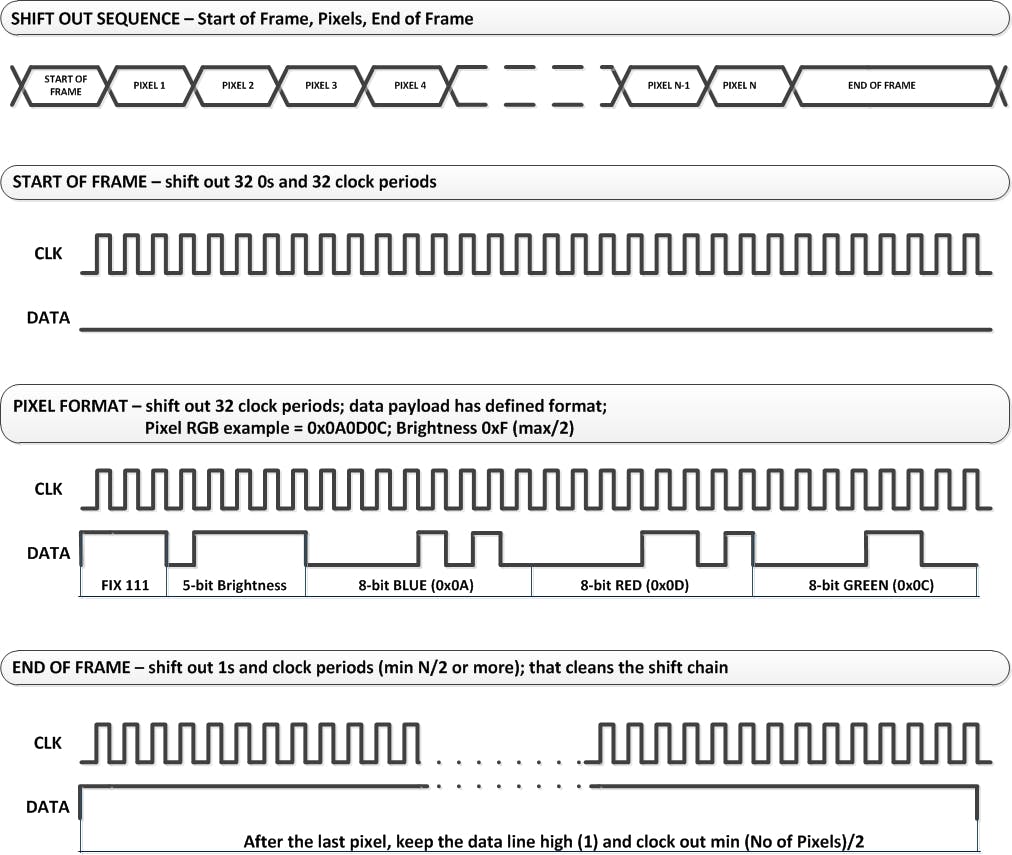

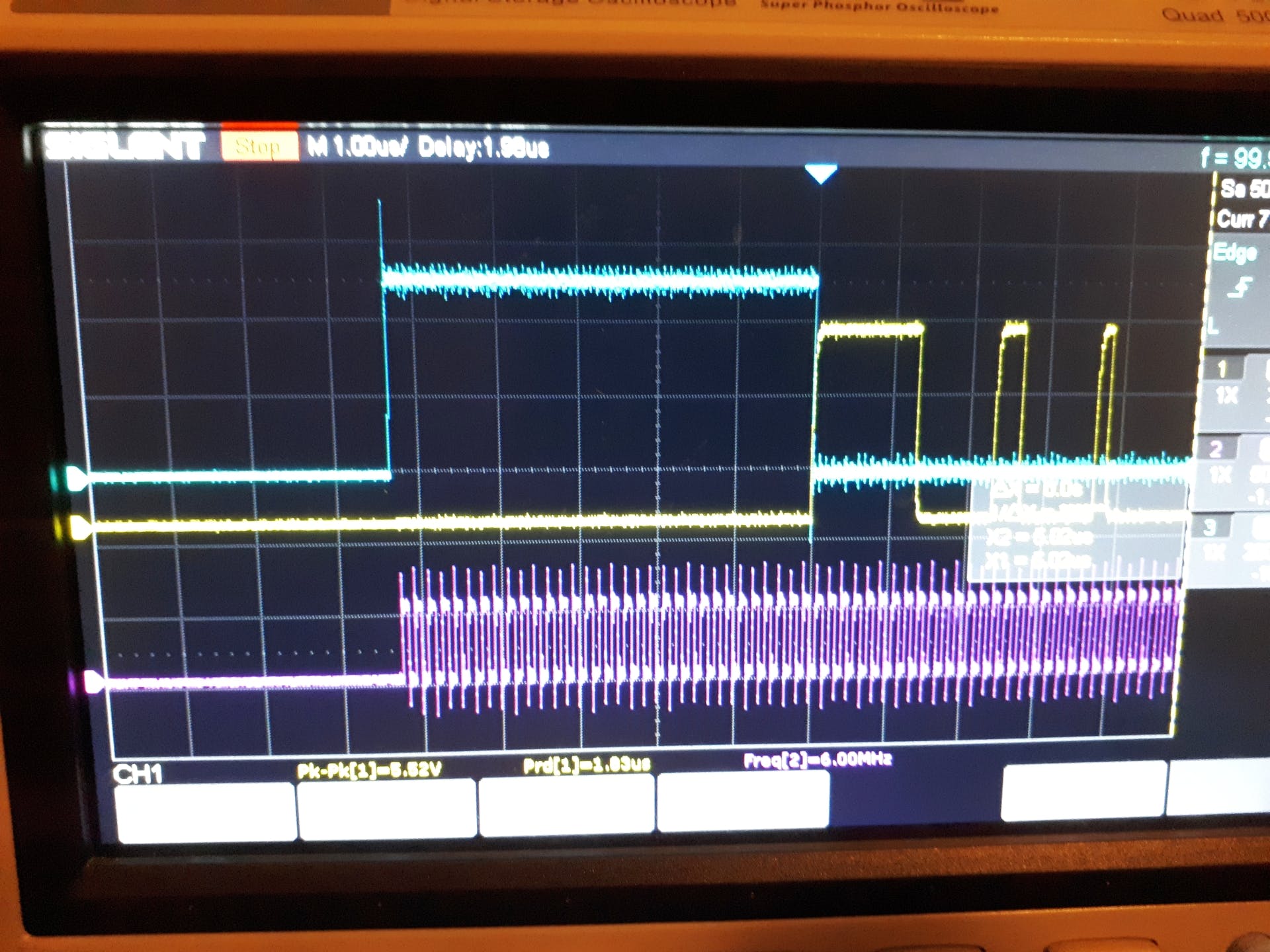

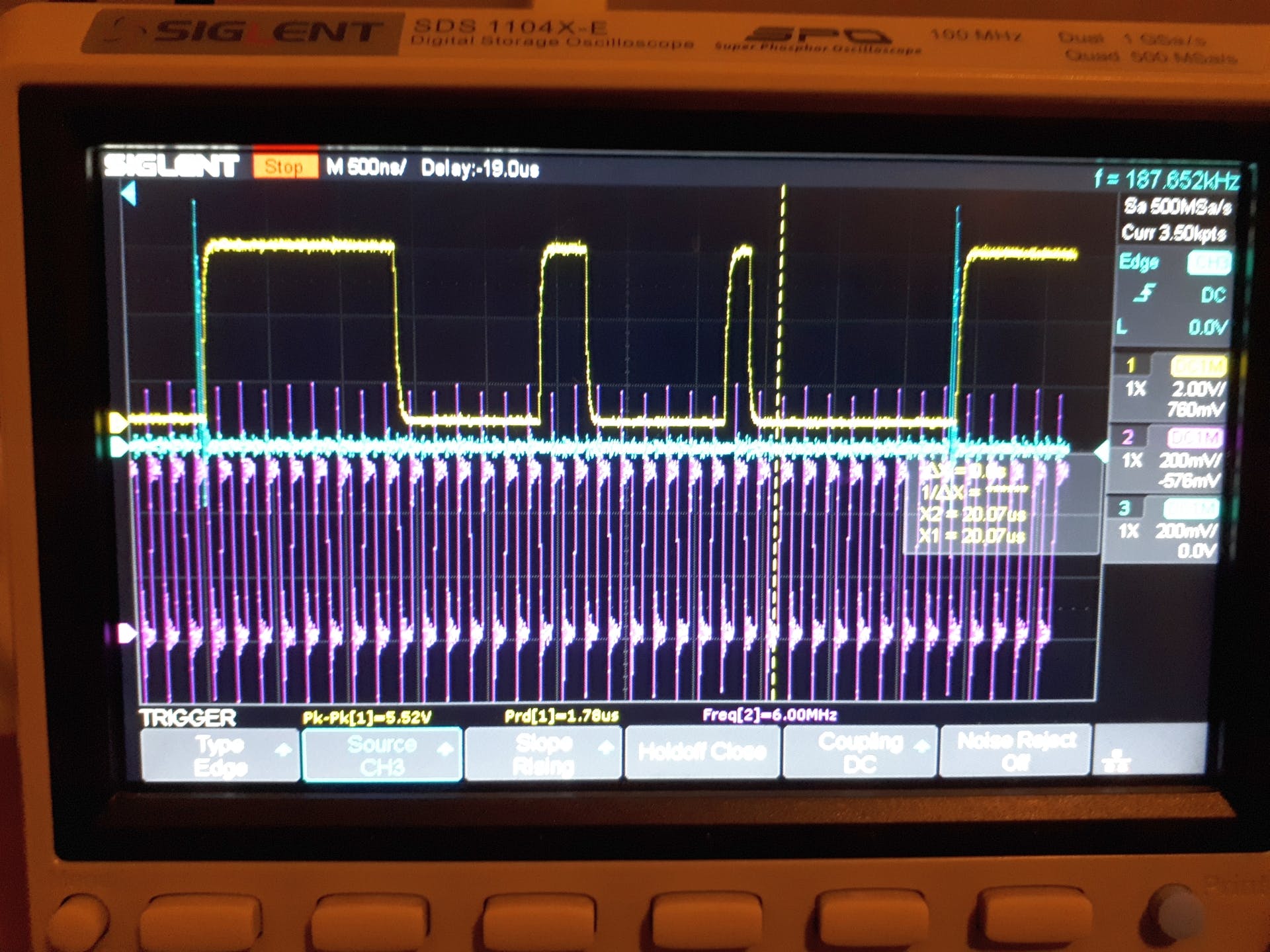

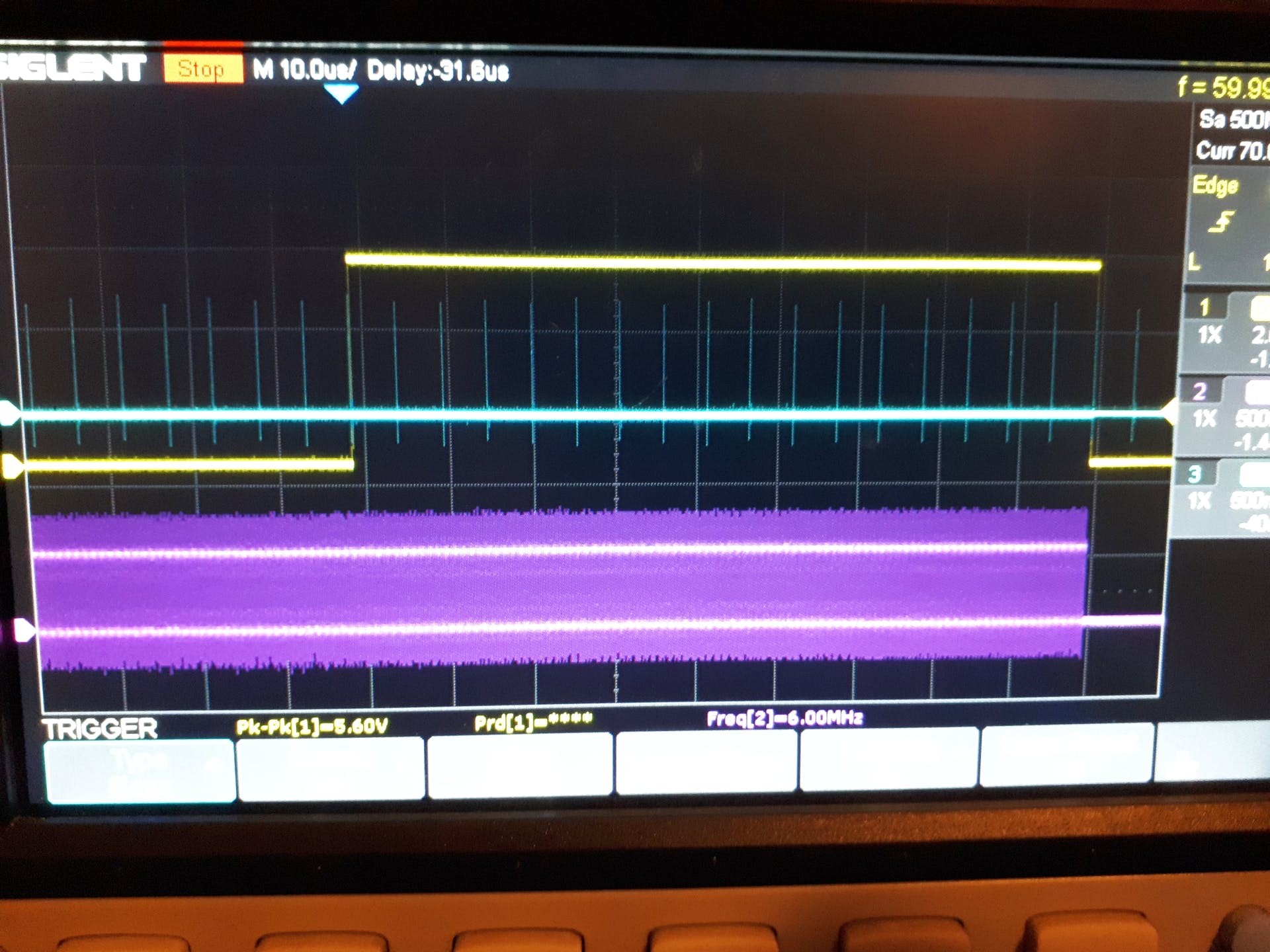

APA102 RGB LED - FPGA视频控制器

消耗积分:0 |

格式:zip |

大小:0.00 MB |

2023-06-29

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章