资料下载

×

电子硬件设计仿真:批量验证神器

消耗积分:1 |

格式:pdf |

大小:1.2M |

2015-04-15

电子硬件设计仿真:批量验证神器

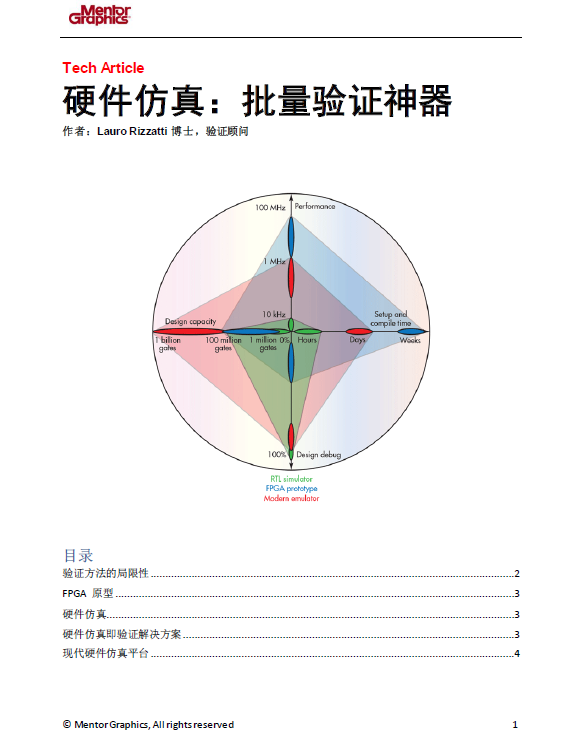

虽然摩尔定律进行了三次修改:现在规定约两年内使集成电路中的晶体管数目增加一倍,但趋势是设计/器件会继续变得越来越大。如今,平均设计尺寸达到或超过 5,000 万专用集成电路 (ASIC) 门,并且有些单个模块已超过 1,000 万门。全球领先的半导体公司的高端设计通常超过 1 亿门。处理器/图形公司的最大设计已达到 10 亿门,或许在不久的将来会超越这一数字。

驱动设计复杂性急剧上升的因素是在现有产品中或在全新设计中添加新特性和新功能的旺盛需求,如果说芯片硬件复杂性骤升得还不够,实现产品差异化的嵌入式软件的暴涨又使验证更为复杂。工程团队难以承受让产品更快推向市场的压力,这迫使其不断创新。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(3)

发评论

-

h1654155854.3559

2015-05-22

0 回复 举报资料很不错啊 收起回复

h1654155854.3559

2015-05-22

0 回复 举报资料很不错啊 收起回复

-

banan613

2015-04-17

0 回复 举报资料太少了吧 1条回复 收起回复

banan613

2015-04-17

0 回复 举报资料太少了吧 1条回复 收起回复 -

0

有需要更详细的资料或更多其他需求,可以加我Q哦~~ kelly:153060836,请加备注:明导白皮书~

全部评论

- 相关下载

- 相关文章