资料下载

×

Reference Design Optimizing FPGA Utilization and Data Throughput for Very High Channel Count Automatic Testers

消耗积分:0 |

格式:pdf |

大小:6.63 MB |

2017-05-02

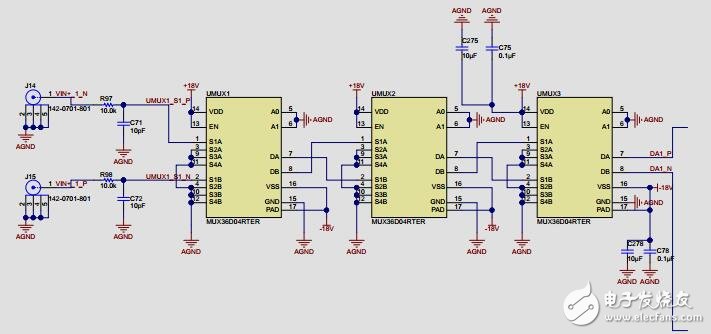

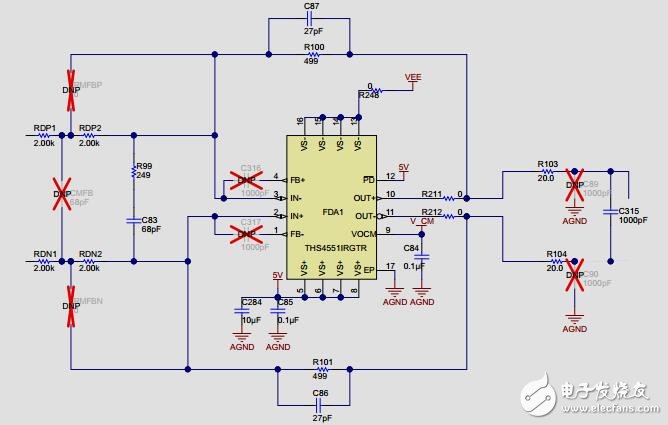

泰德- 01051参考设计用来展示优化通道密度、集成、功耗、时钟分布和信号链的性能非常高的通道数等数据采集(采集)系统自动测试设备中使用的那些(吃)。 使用序列化器,如TI的DS90C383B,结合许多同时采样ADC输出成几个LVDS行可以显著降低针主机FPGA必须处理的数量。 因此,单个FPGA可以处理显著增加数量的采集渠道和董事会路由复杂度大大降低。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章