资料下载

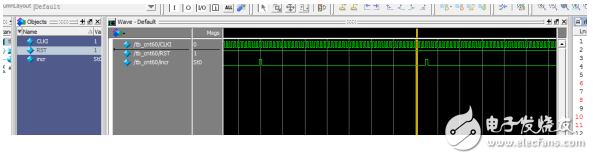

流水线状态机20进制,101序列检测,8位加法器流水线的程序

module count60(rst,clk,incr);

input rst,clk;

output incr;

reg incr;

reg [7:0] cnt;

always@(posedge clk or negedge rst)

begin

if(!rst)

begin

incr 《= 1‘b0;

cnt 《= 8’h0;

end

else if(cnt 》= 59) /*we can set the date ,such as 59 ,actually,is the 6*decimalism; Also, 9 is the decilism;*/

begin

incr 《= 1‘b1;

cnt 《= 8’h0;

end

else

begin

incr 《= 1‘b0;

cnt 《= cnt + 1’b1;

end

end

Endmodule

`timescale 1 ns / 1 ps

module tb_cnt60;

reg CLKI;

reg RST;

wire incr;

initial begin

RST= 1‘b0;

#100

RST= 1’b1;

end

initial begin

CLKI = 1‘b0;

forever # 12.5 CLKI = ~CLKI;

end

count60 cnt_60_inst(.rst(RST),.clk(CLKI ),.incr(incr));

endmodule

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章