资料下载

基于CPLD_ARM的多道脉冲幅度分析器设计

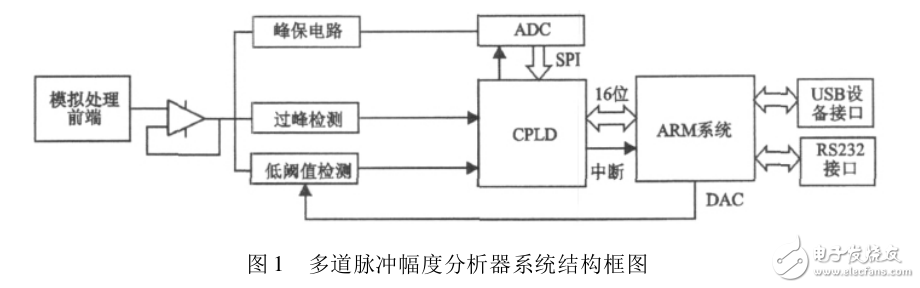

多道脉冲幅度分析器是核探测仪器的重要

组成部分,它把探测器输出的模拟信号转换为

与其峰值成正比的数字信号[1]。传统的多道

脉冲幅度分析器多以 8051 内核单片机构成谱

数据采集控制系统,其硬件电路较复杂,集成度

较低,整体功耗较大,不方便系统升级; 另一方

面,8051 单片机 CPU 的处理性能较弱,在核脉

冲高计数率情况下易产生漏计数的情况,影响

了核脉冲测量的实时性和准确性

随着现代电子技术的快速发展,更多新型

的低功耗、高集成度、高性能器件已被应用于核

能谱采集系统中。32 位 Cortex - M3 ARM 嵌入

式微处理器具有高性能、低功耗的特性,并且提

供了大量的软件参考库,能有效降低软件编程

和调试难度; 新一代 CPLD 芯片具有逻辑资源

丰富、低功耗、易调试等特点,ARM 处理器和

CPLD 器件均已被广泛应用于消费电子产品和

网络通信等诸多领域。它们的出现,也为核能

谱测量系统提高数据处理能力和系统集成度、

降低系统功耗提供了很好的解决方案。为此,

本设 计 以 基 于 Cortex - M3 内 核 的 微 处 理 器

STM32F103ZE 和 MAX - II EPM570 CPLD 器件

为硬件平台,使用 STM32F10x 标准外设库,构

成一种核脉冲数据采集实时性强、集成度高、功

耗低的多道脉冲幅度分析器。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章