资料下载

×

浅谈怎样减少高精度DAC中的加电/断电毛刺脉冲

消耗积分:2 |

格式:rar |

大小:0.8 MB |

2017-11-14

电压毛刺脉冲在信号链路径中很常见,特别在系统加电或断电时更是如此。根据峰值幅度和毛刺脉冲持续时间的不同,系统输出中的最终结果会是灾难性的。其中的一个示例就是工业电机控制系统,在这个系统中,数模转换器 (DAC) 驱动电机驱动器,以控制电机旋转。如果毛刺脉冲幅度高于电机驱动器的灵敏度阈值,当系统加电/断电时,电机会在没有任何方向控制的情况下旋转。

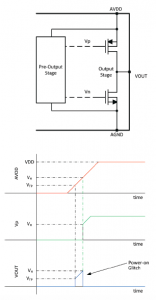

图1.经简化的输出级和加电毛刺脉冲

之前已经分析了高精度DAC经缓冲输出出现加电/断电毛刺脉冲的原因和减少这些毛刺脉冲的解决方案。这份简报主要介绍了DAC输出缓冲器在加电至电压输出模式时出现的加电毛刺脉冲。一个高精度DAC可以在多个配置中加电:零量程、中量程,或是高阻抗。用户可以控制预断电状态。某些DAC具有内置的加电毛刺脉冲减少 (POGR) 电路;这个电路在DAC输出级未被驱动的配置中保持DAC的输出级。经缓冲电压输出DAC具有一对作为输出级的PFET和NFET。POGR电路禁用PFET,并将NFET偏置到其阈值电压 (VTH) 以上,从而最大限度地将加电毛刺脉冲减少到几百毫伏。

并不是每个DAC中都有POGR电路。对于没有POGR的DAC来说,加电/断电毛刺脉冲取决于多个因素:

1.DAC到电压输出模式和高阻抗模式的加电状态

2.DVDD、VREF、IOVDD和其它电源引脚的加电顺序

3.反馈网络连接

4.电源斜升速率

5.输出阻性负载

这篇文章所讨论的是输出级被加电至电压输出模式的情况。在这个模式下,PFET和NFET的栅极由一个预输出级控制。这个预输出级需要一个特定的最小电压来正常启动。这个电压也被称为最小净空 (VH)。这个电压取决于预输出级架构,并且可高至6V。这个电压远远低于数据表中所规定的最小电源电压 (VDDMIN)。通常情况下,大多数数据表中并未指定此电压。

在达到这个最小净空电压前,预输出级没有足够的净空来实现正常运行。因此,输出FET栅极可以低至0V,这使得PFET可以在电源电压与PFET阈值电压 (VTP) 相交时,运行为电源与输出引脚之间的低阻性开关。因此,输出能够随着电源斜升,从而导致了加电毛刺脉冲(请见图1)。

在这个情况下,毛刺脉冲电压可以高达最小净空电压 (VH)。由于预输出级的净空不足,所以这个毛刺脉冲与电源斜升速率无关。所有DAC数据表都规定了一个输出上的最小阻性负载(通常为1kW)。将一个阻性负载加载到DAC输出上是尽可能减小这个毛刺脉冲的常见技术。然而,这项技术并不能最大限度地减少毛刺脉冲幅度,这是因为输出PFET运行为一个电源与输出引脚之间的开关(或短接)。加电序列和反馈网络连接会进一步加大这个毛刺脉冲。由于这些因素通常是相互关联的,它们都作为一种情况进行分析。

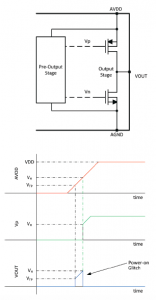

图1.经简化的输出级和加电毛刺脉冲

之前已经分析了高精度DAC经缓冲输出出现加电/断电毛刺脉冲的原因和减少这些毛刺脉冲的解决方案。这份简报主要介绍了DAC输出缓冲器在加电至电压输出模式时出现的加电毛刺脉冲。一个高精度DAC可以在多个配置中加电:零量程、中量程,或是高阻抗。用户可以控制预断电状态。某些DAC具有内置的加电毛刺脉冲减少 (POGR) 电路;这个电路在DAC输出级未被驱动的配置中保持DAC的输出级。经缓冲电压输出DAC具有一对作为输出级的PFET和NFET。POGR电路禁用PFET,并将NFET偏置到其阈值电压 (VTH) 以上,从而最大限度地将加电毛刺脉冲减少到几百毫伏。

并不是每个DAC中都有POGR电路。对于没有POGR的DAC来说,加电/断电毛刺脉冲取决于多个因素:

1.DAC到电压输出模式和高阻抗模式的加电状态

2.DVDD、VREF、IOVDD和其它电源引脚的加电顺序

3.反馈网络连接

4.电源斜升速率

5.输出阻性负载

这篇文章所讨论的是输出级被加电至电压输出模式的情况。在这个模式下,PFET和NFET的栅极由一个预输出级控制。这个预输出级需要一个特定的最小电压来正常启动。这个电压也被称为最小净空 (VH)。这个电压取决于预输出级架构,并且可高至6V。这个电压远远低于数据表中所规定的最小电源电压 (VDDMIN)。通常情况下,大多数数据表中并未指定此电压。

在达到这个最小净空电压前,预输出级没有足够的净空来实现正常运行。因此,输出FET栅极可以低至0V,这使得PFET可以在电源电压与PFET阈值电压 (VTP) 相交时,运行为电源与输出引脚之间的低阻性开关。因此,输出能够随着电源斜升,从而导致了加电毛刺脉冲(请见图1)。

在这个情况下,毛刺脉冲电压可以高达最小净空电压 (VH)。由于预输出级的净空不足,所以这个毛刺脉冲与电源斜升速率无关。所有DAC数据表都规定了一个输出上的最小阻性负载(通常为1kW)。将一个阻性负载加载到DAC输出上是尽可能减小这个毛刺脉冲的常见技术。然而,这项技术并不能最大限度地减少毛刺脉冲幅度,这是因为输出PFET运行为一个电源与输出引脚之间的开关(或短接)。加电序列和反馈网络连接会进一步加大这个毛刺脉冲。由于这些因素通常是相互关联的,它们都作为一种情况进行分析。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章