资料下载

×

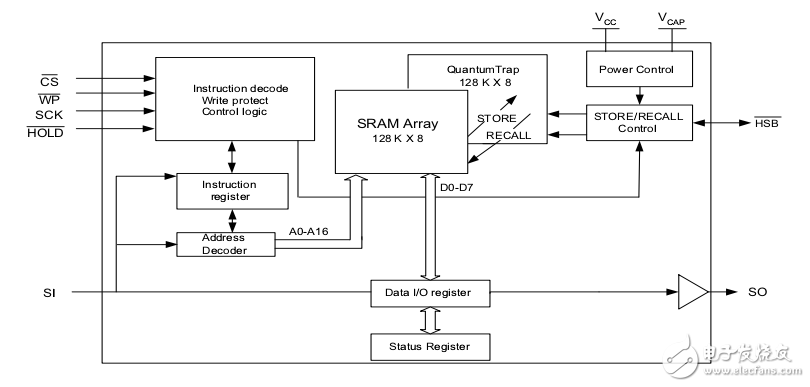

SRAM CY14B101Q1, CY14B101Q2, CY14B101Q3 1 Mbit (128 K × 8) Serial SPI nvSRAM

消耗积分:0 |

格式:rar |

大小:0.54 MB |

2017-10-10

赛普拉斯 CY14B101Q1/CY14B101Q2/CY14B101Q3 将每个存

储单元中具有非易失性组件的 1Mbit nvSRAM 与串行 SPI 接口结

合在一起。 该存储器采用 “128K 字,每字 8 位 ” 的组织方式。 嵌

入式非易失性元件通过采用 QuantumTrap 技术,打造出了世界

上最可靠的非易失性存储器。 SRAM 能够实现无限次读写循环,

而量子井单元则能够提供高度可靠的非易失性数据存储空间。 断

电时,数据会从 SRAM 自动转移到非易失性元件中 (“ 存储 ” 操

作)(CY14B101Q1 除外)。 加电时,数据会从非易失性存储器

回读到 SRAM (“ 回读 ” 操作)。 “ 存储 ” 和 “ 回读 ” 操作也可以

由用户通过 SPI 指令触发。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章